SoC serie Espressif ESP32-C6 Manuale utente Errata

Introduzione

Questo documento descrive gli errori noti nella serie di SoC ESP32-C6.

Questo documento descrive gli errori noti nella serie di SoC ESP32-C6.

Identificazione del chip

Nota:

Controlla il collegamento o il codice QR per assicurarti di utilizzare la versione più recente di questo documento:

https://espressif.com/sites/default/files/documentation/esp32-c6_errata_en.pdf

Controlla il collegamento o il codice QR per assicurarti di utilizzare la versione più recente di questo documento:

https://espressif.com/sites/default/files/documentation/esp32-c6_errata_en.pdf

1 Revisione del chip

Espressif sta introducendo vM.X schema di numerazione per indicare le revisioni del chip.

M – Numero maggiore, che indica la revisione principale del prodotto chip. Se questo numero cambia, significa che il software utilizzato per la versione precedente del prodotto è incompatibile con il nuovo prodotto e la versione del software dovrà essere aggiornata per l'utilizzo del nuovo prodotto.

X – Numero minore, indicante la revisione minore del prodotto chip. Se questo numero cambia, significa che

il software utilizzato per la versione precedente del prodotto è compatibile con il nuovo prodotto e non è necessario aggiornare il software.

il software utilizzato per la versione precedente del prodotto è compatibile con il nuovo prodotto e non è necessario aggiornare il software.

Lo schema vM.X sostituisce gli schemi di revisione del chip utilizzati in precedenza, inclusi i numeri ECOx, Vxxx e altri formati, se presenti.

La revisione del chip è identificata da:

- Campo eFuse EFUSE_RD_MAC_SPI_SYS_3_REG[23:22] e EFUSE_RD_MAC_SPI_SYS_3_REG[21:18]

Tabella 1: Identificazione della revisione del chip tramite bit eFuse

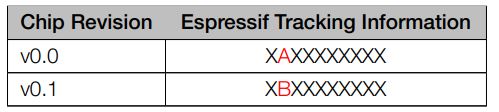

- Informazioni sul tracciamento di Espressif linea nella marcatura del chip

Figura 1: diagramma di marcatura del chip

Tabella 2: Identificazione della revisione del chip mediante marcatura del chip

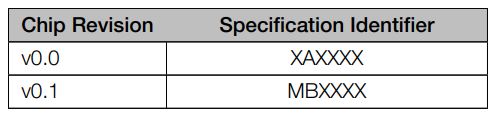

- Identificatore della specifica linea nella marcatura del modulo

Figura 2: diagramma di marcatura del modulo

Tabella 3: Identificazione della revisione del chip in base alla marcatura del modulo

Nota:

- Le informazioni sulla versione ESP-IDF che supporta una specifica revisione del chip sono fornite in Compatibilità tra versioni ESP-IDF e revisioni dei SoC Espressif.

- Per ulteriori informazioni sull'aggiornamento della revisione del chip e sulla relativa identificazione dei prodotti della serie ESP32-C6, fare riferimento a Notifiche di modifica del prodotto/processo ESP32-C6 (PCN).

- Per ulteriori informazioni sullo schema di numerazione delle revisioni dei chip, vedere Avviso di compatibilità per lo schema di numerazione delle revisioni dei chip.

2 metodi aggiuntivi

Alcuni errori nel prodotto del chip non necessitano di essere corretti a livello del silicio, o in altre parole in una nuova revisione del chip.

In questo caso, il chip può essere identificato dal codice data nella marcatura del chip (vedere Figura 1). Per maggiori informazioni,

per favore riferisci a Informazioni sull'imballaggio del chip Espressif.

per favore riferisci a Informazioni sull'imballaggio del chip Espressif.

I moduli costruiti attorno al chip possono essere identificati dal numero PW nell'etichetta del prodotto (vedere Figura 3). Per ulteriori informazioni, fare riferimento a Informazioni sulla confezione del modulo Espressif.

Figura 3: Etichetta del prodotto del modulo

Nota:

Si prega di notare che Numero PW è previsto solo per bobine confezionate in sacchi di alluminio barriera umidità (MBB).

Si prega di notare che Numero PW è previsto solo per bobine confezionate in sacchi di alluminio barriera umidità (MBB).

Descrizione Errata

Tabella 4: Riepilogo degli Errata

3 CPU RISC-V

3.1 Possibile stallo dovuto all'esecuzione fuori ordine delle istruzioni quando è coinvolta la scrittura su LP SRAM

Descrizione

Quando la CPU HP esegue le istruzioni (istruzione A e istruzione B successivamente) nella SRAM LP e l'istruzione A e l'istruzione B seguono i seguenti schemi:

- L'istruzione A prevede la scrittura in memoria. Example: sw/sh/sb

- L'istruzione B implica solo l'accesso al bus delle istruzioni. Exampfile: nop/jal/jalr/lui/auipc

- L'indirizzo dell'istruzione B non è allineato a 4 byte

I dati scritti dall'istruzione A nella memoria vengono salvati solo dopo che l'istruzione B ha completato l'esecuzione. Ciò introduce il rischio per cui, dopo la scrittura dell'istruzione A in memoria, se viene eseguito un ciclo infinito nell'istruzione B, la scrittura dell'istruzione A non verrà mai completata.

soluzioni alternative

Quando riscontri questo problema o quando controlli il codice assembly e vedi il modello sopra menzionato,

- Aggiungi un'istruzione di recinzione tra l'istruzione A e il ciclo infinito. Ciò può essere ottenuto utilizzando l'interfaccia rv_utils_memory_barrier in ESP-IDF.

- Sostituisci il ciclo infinito con l'istruzione wfi. Ciò può essere ottenuto utilizzando l'interfaccia rv_utils_wait_for_intr in ESP-IDF.

- Disabilitare l'estensione RV32C (compressa) durante la compilazione del codice da eseguire nella SRAM LP per evitare istruzioni con indirizzi non allineati a 4 byte.

Soluzione

Da risolvere nelle future revisioni del chip.

Da risolvere nelle future revisioni del chip.

4 Orologio

4.1 Calibrazione imprecisa dell'orologio RC_FAST_CLK

Descrizione

Nel chip ESP32-C6, la frequenza della sorgente di clock RC_FAST_CLK è troppo vicina alla frequenza del clock di riferimento (40 MHz XTAL_CLK), rendendo impossibile una calibrazione accurata. Ciò potrebbe influire sulle periferiche che utilizzano RC_FAST_CLK e hanno requisiti rigorosi per la sua frequenza di clock precisa.

Per le periferiche che utilizzano RC_FAST_CLK, fare riferimento al Manuale di riferimento tecnico ESP32-C6 > Capitolo Reset e orologio.

soluzioni alternative

Utilizza altre sorgenti di clock invece di RC_FAST_CLK.

Utilizza altre sorgenti di clock invece di RC_FAST_CLK.

Soluzione

Risolto il problema con la revisione del chip v0.1.

Risolto il problema con la revisione del chip v0.1.

5 Ripristino

5.1 Il ripristino del sistema attivato dal timer watchdog RTC non può essere segnalato correttamente

Descrizione

Quando il timer watchdog RTC (RWDT) attiva un ripristino del sistema, il codice sorgente di ripristino non può essere bloccato correttamente. Di conseguenza, la causa del ripristino segnalata è indeterminata e potrebbe essere errata.

Quando il timer watchdog RTC (RWDT) attiva un ripristino del sistema, il codice sorgente di ripristino non può essere bloccato correttamente. Di conseguenza, la causa del ripristino segnalata è indeterminata e potrebbe essere errata.

soluzioni alternative

Nessuna soluzione alternativa.

Nessuna soluzione alternativa.

Soluzione

Risolto il problema con la revisione del chip v0.1.

Risolto il problema con la revisione del chip v0.1.

6RMT

6.1 Il livello del segnale in stato di inattività potrebbe presentare errori nella modalità TX continua RMT

Descrizione

Nel modulo RMT di ESP32-C6, se la modalità TX continua è abilitata, si prevede che la trasmissione dei dati si interrompa dopo che i dati sono stati inviati per RMT_TX_LOOP_NUM_CHn round e, successivamente, il livello del segnale in stato di inattività dovrebbe essere controllato dal "livello" campo dell'end-marker.

Nel modulo RMT di ESP32-C6, se la modalità TX continua è abilitata, si prevede che la trasmissione dei dati si interrompa dopo che i dati sono stati inviati per RMT_TX_LOOP_NUM_CHn round e, successivamente, il livello del segnale in stato di inattività dovrebbe essere controllato dal "livello" campo dell'end-marker.

Tuttavia, nella situazione reale, dopo l'interruzione della trasmissione dei dati, il livello del segnale dello stato inattivo del canale non è controllato dal campo "livello" dell'indicatore finale, ma dal livello nei dati riportati, che è indeterminato.

soluzioni alternative

Si consiglia agli utenti di impostare RMT_IDLE_OUT_EN_CHn su 1 per utilizzare solo i registri per controllare il livello di inattività.

Questo problema è stato aggirato dalla prima versione ESP-IDF che supporta la modalità TX continua (v5.1). In queste versioni di ESP-IDF è configurato che il livello di minimo possa essere controllato solo tramite registri.

Si consiglia agli utenti di impostare RMT_IDLE_OUT_EN_CHn su 1 per utilizzare solo i registri per controllare il livello di inattività.

Questo problema è stato aggirato dalla prima versione ESP-IDF che supporta la modalità TX continua (v5.1). In queste versioni di ESP-IDF è configurato che il livello di minimo possa essere controllato solo tramite registri.

Soluzione

Nessuna correzione pianificata.

Nessuna correzione pianificata.

7 Wi-Fi

7.1 ESP32-C6 Non può essere un iniziatore FTM 802.11mc

Descrizione

L'ora di T3 (ovvero l'ora di partenza dell'ACK dall'iniziatore) utilizzata nella misurazione del tempo fine (FTM) 802.11mc non può essere acquisita correttamente e di conseguenza ESP32-C6 non può essere l'iniziatore FTM.

L'ora di T3 (ovvero l'ora di partenza dell'ACK dall'iniziatore) utilizzata nella misurazione del tempo fine (FTM) 802.11mc non può essere acquisita correttamente e di conseguenza ESP32-C6 non può essere l'iniziatore FTM.

soluzioni alternative

Nessuna soluzione alternativa.

Nessuna soluzione alternativa.

Soluzione

Da risolvere nelle future revisioni del chip.

Da risolvere nelle future revisioni del chip.

Documentazione correlata

- Scheda tecnica della serie ESP32-C6: specifiche dell'hardware ESP32-C6.

- Manuale di riferimento tecnico ESP32-C6: informazioni dettagliate su come utilizzare la memoria e le periferiche ESP32-C6.

- Linee guida per la progettazione hardware ESP32-C6: linee guida su come integrare ESP32-C6 nel prodotto hardware.

- Certificati https://espressif.com/en/support/documents/certificates

- Notifiche di modifica del prodotto/processo ESP32-C6 (PCN) https://espressif.com/en/support/documents/pcns?keys=ESP8684

- Aggiornamenti della documentazione e sottoscrizione delle notifiche di aggiornamento https://espressif.com/en/support/download/documents

Zona Sviluppatore

- Guida alla programmazione ESP-IDF per ESP32-C6: documentazione estesa per il framework di sviluppo ESP-IDF.

- ESP-IDF e altri framework di sviluppo su GitHub.

https://github.com/espressif - Forum ESP32 BBS – Community Engineer-to-Engineer (E2E) per i prodotti Espressif in cui è possibile inviare domande, condividere conoscenze, esplorare idee e aiutare a risolvere problemi con altri ingegneri.

https://esp32.com/ - L'ESP Journal - Migliori pratiche, articoli e note di persone di Espressif.

https://blog.espressif.com/ - Vedi le schede SDK e demo, App, Strumenti, Firmware AT.

https://espressif.com/en/support/download/sdks-demos

Prodotti

- SoC serie ESP32-C6: sfoglia tutti i SoC ESP32-C6.

https://espressif.com/en/products/socs?id=ESP32-C6 - Moduli della serie ESP32-C6: sfoglia tutti i moduli basati su ESP32-C6.

https://espressif.com/en/products/modules?id=ESP32-C6 - DevKit serie ESP32-C6: sfoglia tutti i devkit basati su ESP32-C6.

https://espressif.com/en/products/devkits?id=ESP32-C6 - Selettore prodotti ESP: trova un prodotto hardware Espressif adatto alle tue esigenze confrontando o applicando filtri.

https://products.espressif.com/#/product-selector?language=en

Contattaci

- Vedere le schede Domande di vendita, Richieste tecniche, Schema di circuito e PCB Design Review, Prendeamples

(Negozi online), Diventa nostro fornitore, Commenti e suggerimenti.

https://espressif.com/en/contact-us/sales-questions

Cronologia delle revisioni

Dichiarazione di non responsabilità e avviso sul copyright

Informazioni in questo documento, incluso URL riferimenti, è soggetto a modifiche senza preavviso.

TUTTE LE INFORMAZIONI DI TERZE PARTI IN QUESTO DOCUMENTO SONO FORNITE COME SENZA GARANZIE DI AUTENTICITÀ E ACCURATEZZA.

NESSUNA GARANZIA VIENE FORNITA AL PRESENTE DOCUMENTO PER LA SUA COMMERCIABILITÀ, NON VIOLAZIONE, IDONEITÀ PER QUALSIASI SCOPO PARTICOLARE, NÉ ALCUNA GARANZIA ALTRIMENTI DERIVANTE DA QUALSIASI PROPOSTA, SPECIFICA O SAMPLE.

Si declina ogni responsabilità, inclusa la responsabilità per violazione di qualsiasi diritto di proprietà, relativa all'uso delle informazioni in questo documento. Nessuna licenza espressa o implicita, per preclusione o altro, su alcun diritto di proprietà intellettuale è concessa nel presente documento.

Il logo Wi-Fi Alliance Member è un marchio di Wi-Fi Alliance. Il logo Bluetooth è un marchio registrato di Bluetooth SIG.

Tutti i nomi commerciali, marchi e marchi registrati citati in questo documento sono di proprietà dei rispettivi proprietari e vengono qui riconosciuti.

Copyright © 2023 Espressif Systems (Shanghai) Co., Ltd. Tutti i diritti riservati.

Informazioni in questo documento, incluso URL riferimenti, è soggetto a modifiche senza preavviso.

TUTTE LE INFORMAZIONI DI TERZE PARTI IN QUESTO DOCUMENTO SONO FORNITE COME SENZA GARANZIE DI AUTENTICITÀ E ACCURATEZZA.

NESSUNA GARANZIA VIENE FORNITA AL PRESENTE DOCUMENTO PER LA SUA COMMERCIABILITÀ, NON VIOLAZIONE, IDONEITÀ PER QUALSIASI SCOPO PARTICOLARE, NÉ ALCUNA GARANZIA ALTRIMENTI DERIVANTE DA QUALSIASI PROPOSTA, SPECIFICA O SAMPLE.

Si declina ogni responsabilità, inclusa la responsabilità per violazione di qualsiasi diritto di proprietà, relativa all'uso delle informazioni in questo documento. Nessuna licenza espressa o implicita, per preclusione o altro, su alcun diritto di proprietà intellettuale è concessa nel presente documento.

Il logo Wi-Fi Alliance Member è un marchio di Wi-Fi Alliance. Il logo Bluetooth è un marchio registrato di Bluetooth SIG.

Tutti i nomi commerciali, marchi e marchi registrati citati in questo documento sono di proprietà dei rispettivi proprietari e vengono qui riconosciuti.

Copyright © 2023 Espressif Systems (Shanghai) Co., Ltd. Tutti i diritti riservati.

Documenti / Risorse

|

Errata SoC serie Espressif ESP32-C6 [pdf] Manuale d'uso Errata SoC serie ESP32-C6, Errata SoC serie ESP32-C6, Errata |