Intel Agilex Logic Array Blocks e Adaptive Logic Modules

Intel® Agilex™ LAB e ALM Terminatiview

Il blocco array logico (LAB) è composto da blocchi di base noti come moduli logici adattativi (ALM). È possibile configurare i LAB per implementare funzioni logiche, funzioni aritmetiche e funzioni di registro.

Puoi utilizzare metà dei LAB disponibili nei dispositivi Intel® Agilex™ come LAB di memoria (MLAB). Alcuni dispositivi possono avere un rapporto MLAB più elevato.

Il software Intel Quartus® Prime e altri strumenti di sintesi di terze parti supportati scelgono automaticamente la modalità appropriata per funzioni comuni come contatori, sommatori, sottrattori e funzioni aritmetiche.

Architettura Intel Hyperflex™ Core, Dispositivo Intel Agilex Overview

Fornisce ulteriori informazioni su Hyper-Registers e sull'architettura di base Intel Hyperflex™. Gli Hyper-Registers sono registri aggiuntivi disponibili in ogni segmento di instradamento di interconnessione in tutto il core fabric, inclusi i segmenti di instradamento collegati agli input e agli output LAB.

Registro Intel Hyperflex™

La famiglia di dispositivi Intel Agilex si basa sull'architettura di base Intel Hyperflex™.

Intel Agilex LAB contiene i registri Intel Hyperflex e altre funzionalità progettate per facilitare il retiming. I registri Intel Hyperflex sono disponibili negli ALM e nelle catene di trasporto. Come mostrato nella figura Intel Agilex ALM Connection Details, i registri Intel Hyperflex si trovano sugli ingressi sincroni Clear e Clock Enable per aumentare o ridurre il ritardo del percorso. Tutti i registri Intel Hyperflex possono essere abilitati e sono controllati dal software Intel Quartus Prime durante il retiming.

Architettura e caratteristiche di Intel Agilex LAB e ALM

Le sezioni seguenti descrivono il LAB e l'ALM per i dispositivi Intel Agilex.

LABORATORIO

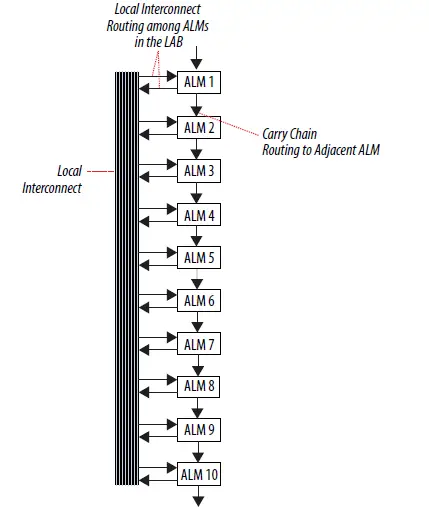

I LAB sono blocchi logici configurabili costituiti da un gruppo di risorse logiche. Ogni LAB contiene una logica dedicata per indirizzare i segnali di controllo ai propri ALM. Il MLAB è un superset del LAB e include tutte le funzionalità del LAB. Ci sono un totale di 10 ALM in ogni LAB, come mostrato nella figura Intel Agilex LAB e MLAB Structure.

Figura 1.

Intel Agilex LAB Struttura e interconnessioni finiteview

Questa cifra mostra un overview della struttura Intel Agilex LAB e MLAB con le interconnessioni LAB.

Informazioni correlate

Informazioni correlate

MLAB a pagina 6

MLAB

Ogni MLAB supporta un massimo di 640 bit di semplice SRAM dual-port. È possibile configurare ogni ALM in un MLAB come un blocco di memoria di 32 (profondità) x 2 (larghezza), ottenendo una configurazione di 32 (profondità) x 20 (larghezza) semplice blocco SRAM a doppia porta.

Figura 2.

Struttura Intel Agilex LAB e MLAB Interconnessioni locali e di collegamento diretto

Interconnessioni locali e di collegamento diretto

Ogni LAB può pilotare 60 uscite ALM. Un sottoinsieme di questi può guidare direttamente gli input LAB, ma qualsiasi connessione a una riga o colonna diversa deve utilizzare almeno un cavo di instradamento generico.

L'interconnessione locale guida gli ingressi ALM. Le uscite ALM, così come le interconnessioni di riga e colonna, guidano l'interconnessione locale.

Figura 3. Interconnessione Intel Agilex LAB Local e Direct Link  Portare interconnessioni a catena

Portare interconnessioni a catena

Esiste un percorso della catena di trasporto dedicato tra gli ALM. I dispositivi Intel Agilex includono una struttura di interconnessione avanzata nei LAB per l'instradamento delle catene di trasporto per funzioni aritmetiche efficienti. Queste connessioni da ALM a ALM ignorano l'interconnessione locale.

I registri Intel Hyperflex vengono aggiunti alla catena di trasporto per consentire un retiming flessibile attraverso una catena di LAB e il compilatore Intel Quartus Prime ne approfitta automaticamentetage di queste risorse per migliorare l'utilizzo e le prestazioni.

Figura 4. Portare interconnessioni a catena Segnali di controllo LAB

Segnali di controllo LAB

Ci sono due sorgenti di clock in ciascun blocco di controllo LAB, che generano due clock LAB (LABCLK[1:0]) e due clock LAB ritardati (LABCLK_Phi1[1:0]) per pilotare i registri ALM e gli Hyper-Registers nel LAB. Il LAB supporta due segnali di abilitazione del clock univoci, oltre a segnali di cancellazione aggiuntivi, per i registri ALM.

I clock di riga LAB [5..0] e le interconnessioni locali LAB generano i segnali di controllo a livello di LAB. Una rete di clock a bassa inclinazione distribuisce segnali globali ai clock di riga [5..0]. L'interconnessione MultiTrack è costituita da linee di instradamento continue e ottimizzate per le prestazioni di diverse lunghezze e velocità utilizzate per l'efficienza dell'instradamento. Il compilatore Intel Quartus Prime indirizza automaticamente i percorsi di progettazione critici su interconnessioni più veloci per migliorare le prestazioni di progettazione e ottimizzare le risorse del dispositivo.

Chiaro controllo logico

I segnali a livello di LAB controllano la logica per il segnale in chiaro del registro ALM. Il registro ALM supporta direttamente sia una cancellazione sincrona che asincrona. Ogni LAB supporta un segnale chiaro sincrono e due segnali chiari asincroni.

I dispositivi Intel Agilex forniscono un pin di ripristino a livello di dispositivo (DEV_CLRn) che reimposta tutti i registri nel dispositivo. È possibile abilitare il pin DEV_CLRn nel software Intel Quartus Prime prima della compilazione. Il segnale di ripristino a livello di dispositivo esclude tutti gli altri segnali di controllo.

Figura 5. Segnali di controllo Intel Agilex LAB-Wide

ALM

Le seguenti sezioni trattano le risorse ALM, l'output ALM e le modalità operative ALM.

Risorse dell'ALM

Ogni ALM contiene una varietà di risorse basate su LUT che possono essere suddivise tra due LUT adattive combinatorie (ALUT), un sommatore completo a due bit e quattro registri.

Con un massimo di otto ingressi per i due ALUT combinatori, un ALM può implementare varie combinazioni di due funzioni. Questa adattabilità consente a un ALM di essere completamente retrocompatibile con quattro architetture LUT di input. Un ALM può anche implementare un sottoinsieme di otto funzioni di ingresso.

Un ALM contiene quattro registri programmabili. Ogni registro ha le seguenti porte:

- Dati in

- Dati fuori

- Normale orologio LAB

- Orologio LAB ritardato

- Abilitazione orologio

- Sincrono chiaro

- Chiaro asincrono

I segnali globali, i pin I/O generici (GPIO) o qualsiasi logica interna possono guidare il segnale di abilitazione del clock, il clock e i segnali di controllo chiaro asincroni o sincroni di un registro ALM. Il segnale di abilitazione dell'orologio ha la priorità sul segnale di ripristino sincrono.

Per le funzioni combinatorie, i registri vengono bypassati e l'uscita della tabella di ricerca (LUT) e dei sommatori passa direttamente alle uscite di un ALM. Sono disponibili due uscite veloci per 6 uscite LUT e 5 uscite LUT inferiori per bypassare il mux di uscita e connettersi a un altro LAB per la regolazione del percorso critico.

Figura 6. Diagramma a blocchi di alto livello di Intel Agilex ALM

Uscita ALM

Uscita ALM

Gli output di instradamento generale in ogni ALM guidano le risorse di instradamento locale, di riga e di colonna. Sei uscite ALM, inclusi due percorsi di uscita veloci, possono guidare connessioni di instradamento di colonna, riga o collegamento diretto.

L'uscita LUT, sommatore o registro può pilotare le uscite ALM. Sia la LUT o il sommatore che il registro ALM possono uscire simultaneamente dall'ALM.

L'impacchettamento dei registri migliora l'utilizzo del dispositivo consentendo di impacchettare registri non correlati e logica combinatoria in un singolo ALM. L'ALM può anche eliminare le versioni registrate e non registrate dell'uscita LUT o del sommatore.

La figura seguente mostra la connettività Intel Agilex ALM. In Intel Quartus Prime Resource Property Editor, l'intera connessione ALM è semplificata. Alcuni instradamenti verranno instradati internamente dal software Intel Quartus Prime.

Figura 7. Dettagli di connessione Intel Agilex ALM Modalità operative dell'ALM

Modalità operative dell'ALM

Intel Agilex ALM funziona in una delle seguenti modalità:

- Modalità normale

- Modalità LUT estesa

- Modalità aritmetica

Modalità normale

La modalità normale consente di implementare due funzioni in un Intel Agilex ALM o una singola funzione fino a sei ingressi.

Fino a otto input di dati dall'interconnessione locale LAB sono input per la logica combinatoria.

L'ALM può supportare determinate combinazioni di funzioni completamente indipendenti e varie combinazioni di funzioni che hanno input comuni.

Il compilatore Intel Quartus Prime seleziona automaticamente gli input per la LUT. Gli ALM in modalità normale supportano l'impacchettamento dei registri.

La figura seguente mostra una combinazione di diverse connessioni di ingresso per la modalità LUT. Nel progetto, il software Intel Quartus Prime può assegnare diversi nomi di input durante la compilazione.

Figura 8. ALM in modalità normale

Sono supportate anche combinazioni di funzioni con meno input rispetto a quelle mostrate. Per esample, sono supportate combinazioni di funzioni con il seguente numero di ingressi.

- 4 e 3

- 3 e 3

- 3 e 2

- 5 e 2

Per raggruppare due funzioni a 5 ingressi in un ALM, le funzioni devono avere almeno due ingressi comuni. Gli input comuni sono dataa e datab. La combinazione di una funzione a 4 ingressi con una funzione a 5 ingressi richiede un ingresso comune (dataa o datab).

In un dispositivo scarsamente utilizzato, le funzioni che potrebbero essere collocate in un ALM possono essere implementate in ALM separati dal software Intel Quartus Prime per ottenere le migliori prestazioni possibili. Quando un dispositivo inizia a riempirsi, il software Intel Quartus Prime utilizza automaticamente tutto il potenziale di Intel Agilex ALM. Il compilatore Intel Quartus Prime cerca automaticamente le funzioni utilizzando input comuni o funzioni completamente indipendenti da inserire in un ALM per utilizzare in modo efficiente le risorse del dispositivo. Inoltre, puoi controllare manualmente l'utilizzo delle risorse impostando le assegnazioni di posizione.

Figura 9. Funzione modalità LUT a 6 ingressi in modalità normale

Figura 10. Funzione modalità LUT a 3 ingressi in modalità normale

Figura 10. Funzione modalità LUT a 3 ingressi in modalità normale

i dati e i dati b sono disponibili per l'imballo a registro.  È possibile implementare qualsiasi funzione da tre a sei input utilizzando i seguenti input:

È possibile implementare qualsiasi funzione da tre a sei input utilizzando i seguenti input:

- dati

- datad0

- datac0

- datac1

- datad1

- dataf

- dataa e datab, in cui dataa e datab sono condivisi tra entrambe le LUT per fornire flessibilità per implementare una funzione diversa in ciascuna LUT.

Entrambi gli input dataa e datab supportano la funzione di impacchettamento dei registri. Se si abilita la funzione di impacchettamento del registro, entrambi gli ingressi dataa e datab o uno degli ingressi ignorano la LUT e si inseriscono direttamente nel registro, a seconda della modalità di registro impacchettata utilizzata. Per i dispositivi Intel Agilex, sono supportati i seguenti tipi di modalità di registrazione compressi:

- LUT a 5 ingressi con 1 percorso di registro compresso

- LUT a 5 ingressi con 2 percorsi di registro compressi

- Due LUT a 3 ingressi con 2 percorsi di registro compressi

La LUT a 3 ingressi con 2 percorsi di registro compressi è illustrata nella figura Funzione modalità LUT a 3 ingressi in modalità normale. Per i dispositivi Intel Agilex, la modalità LUT a 6 input non supporta la funzionalità di impacchettamento dei registri.

Modalità LUT estesa

Figura 11. Funzioni a 8 ingressi supportate nella modalità LUT estesa

Alcune funzioni a 8 ingressi possono essere implementate in un singolo ALM utilizzando tutti gli ingressi LUT:

- dati

- datad0

- datac0

- dati

- banca dati

- datac1

- datad1

- dataf

Nella modalità LUT estesa a 8 ingressi, è supportata la modalità registro compresso, a condizione che il registro compresso condivida un ingresso dataa o datab con la LUT a 8 ingressi.

Modalità aritmetica

L'ALM in modalità aritmetica utilizza due serie di due LUT a 4 ingressi insieme a due sommatori completi dedicati. I sommatori dedicati consentono alle LUT di eseguire la logica pre-sommatore. Pertanto, ogni sommatore può sommare l'output di due funzioni a 4 ingressi.

La modalità aritmetica offre anche l'abilitazione dell'orologio, l'abilitazione del contatore, il controllo sincrono su e giù, il controllo addizione e sottrazione e la cancellazione sincrona.

Le opzioni clear e clock enable sono segnali a livello di LAB che influenzano tutti i registri nel LAB. È possibile disabilitare o abilitare individualmente questi segnali per ciascuna coppia di registri in una LUT adattiva (ALUT). Il software Intel Quartus Prime posiziona automaticamente tutti i registri che non vengono utilizzati dal contatore in altri LAB.

Figura 12. Intel Agilex ALM in modalità aritmetica

Catena per il trasporto

Catena per il trasporto

La catena di trasporto fornisce una funzione di trasporto veloce tra i sommatori dedicati nella modalità aritmetica.

La funzione di selezione del trasporto a 2 bit nei dispositivi Intel Agilex suddivide il ritardo di propagazione delle catene di trasporto con l'ALM. Le catene di riporto possono iniziare nel primo ALM o nel sesto ALM in un LAB. Il segnale di riporto finale viene indirizzato a un ALM, dove viene inviato alle interconnessioni locali, di riga o di colonna.

Cronologia delle revisioni del documento per la guida dell'utente dei blocchi dell'array logico Intel Agilex e dei moduli logici adattivi

| Versione del documento | Cambiamenti |

| 2022.05.24 | Figura aggiornata: diagramma a blocchi di alto livello di Intel Agilex ALM. |

| 2019.11.14 | Aggiornata la descrizione nella sezione Segnali di controllo LAB. |

| 2019.10.01 |

|

| 2019.04.02 | Versione iniziale. |

Società Intel.

Tutti i diritti riservati. Intel, il logo Intel e altri marchi Intel sono marchi di Intel Corporation o delle sue consociate. Intel garantisce le prestazioni dei suoi prodotti FPGA e semiconduttori in base alle specifiche correnti in conformità con la garanzia standard di Intel, ma si riserva il diritto di apportare modifiche a qualsiasi prodotto e servizio in qualsiasi momento senza preavviso. Intel non si assume alcuna responsabilità derivante dall'applicazione o dall'uso di informazioni, prodotti o servizi qui descritti, salvo quanto espressamente concordato per iscritto da Intel. Si consiglia ai clienti Intel di ottenere la versione più recente delle specifiche del dispositivo prima di fare affidamento su qualsiasi informazione pubblicata e prima di effettuare ordini per prodotti o servizi.

*Altri nomi e marchi potrebbero essere rivendicati come proprietà di terzi.

ISO

9001:2015

Registrato

Documenti / Risorse

|

Intel Agilex Logic Array Blocks e Adaptive Logic Modules [pdf] Guida utente Agilex Logic Array Blocks e Adaptive Logic Modules, Agilex, Logic Array Blocks e Adaptive Logic Modules, Array Blocks e Adaptive Logic Modules, Adaptive Logic Modules, Logic Modules |