Intel AN 805 Riconfigurazione parziale gerarchica di un progetto sulla scheda di sviluppo SoC Arria 10

Tutorial sulla riconfigurazione parziale gerarchica per la scheda di sviluppo SoC Intel® Arria® 10

Questa nota applicativa illustra la trasformazione di un progetto semplice in un progetto parzialmente riconfigurabile gerarchicamente e l'implementazione del progetto sulla scheda di sviluppo SoC Intel® Arria® 10. La riconfigurazione parziale gerarchica (HPR) è un tipo speciale di riconfigurazione parziale (PR), in cui si contiene una regione PR all'interno di un'altra regione PR. È possibile creare più identità sia per la partizione secondaria che per quella principale. Nidifica le partizioni figlie all'interno delle rispettive partizioni madri. La riconfigurazione di una partizione figlio non influisce sul funzionamento nelle regioni padre o statiche. La riconfigurazione di una partizione principale non influisce sull'operazione nella regione statica, ma sostituisce le partizioni secondarie della regione principale con personaggi della partizione secondaria predefiniti. Questa metodologia è efficace nei sistemi in cui più funzioni condividono nel tempo le stesse risorse del dispositivo FPGA.

La riconfigurazione parziale fornisce i seguenti miglioramenti alla progettazione piatta:

- Consente la riconfigurazione della progettazione in fase di esecuzione

- Aumenta la scalabilità del progetto

- Riduce i tempi di inattività del sistema

- Supporta funzioni di multiplexing temporale dinamico nella progettazione

- Riduce i costi e il consumo energetico attraverso un uso efficiente dello spazio sulla scheda

- Nota:

- L'implementazione di questo progetto di riferimento richiede una familiarità di base con il flusso di implementazione dell'FPGA Intel Quartus® Prime e la conoscenza del progetto Intel Quartus Prime primario files.

Informazioni correlate

- Guida per l'utente del kit di sviluppo SoC Intel Arria 10

- Concetti di riconfigurazione parziale

- Flusso di progettazione della riconfigurazione parziale

- Raccomandazioni per la progettazione di riconfigurazione parziale

- Considerazioni sulla progettazione della riconfigurazione parziale

Requisiti di progettazione di riferimento

Questo progetto di riferimento richiede quanto segue:

- Software Intel Quartus Prime Pro Edition versione 17.1 per l'implementazione della progettazione.

- Kit di sviluppo SoC Intel Arria 10 per l'implementazione FPGA.

Società Intel. Tutti i diritti riservati. Intel, il logo Intel e altri marchi Intel sono marchi di Intel Corporation o delle sue consociate. Intel garantisce le prestazioni dei suoi prodotti FPGA e semiconduttori in base alle specifiche correnti in conformità con la garanzia standard di Intel, ma si riserva il diritto di apportare modifiche a qualsiasi prodotto e servizio in qualsiasi momento senza preavviso. Intel non si assume alcuna responsabilità derivante dall'applicazione o dall'uso di informazioni, prodotti o servizi qui descritti, salvo quanto espressamente concordato per iscritto da Intel. Si consiglia ai clienti Intel di ottenere la versione più recente delle specifiche del dispositivo prima di fare affidamento su qualsiasi informazione pubblicata e prima di effettuare ordini per prodotti o servizi.

- Altri nomi e marchi potrebbero essere rivendicati come proprietà di terzi.

Progetto di riferimento terminatoview

- Questo progetto di riferimento è costituito da un contatore a 32 bit. A livello di scheda, il progetto collega il clock a una sorgente da 50 MHz e collega l'uscita a quattro LED sull'FPGA. Selezionando l'uscita dai bit del contatore in una sequenza specifica, i LED lampeggiano con una frequenza specifica.

Figura 1. Progetto di riferimento piatto senza partizionamento PR

Progetto di riferimento Files

L'esercitazione sulla riconfigurazione parziale è disponibile nel seguente percorso: https://github.com/intel/fpga-partial-reconfig

Per scaricare il tutorial:

- Fai clic su Clona o scarica.

- Fare clic su Scarica ZIP. Decomprimere FPGA-partial-config-master.zip file.

- Passare alla sottocartella tutorials/a10_soc_devkit_blinking_led_hpr per accedere al progetto di riferimento.

La cartella piatta è composta da quanto segue files:

Tabella 1. Progetto di riferimento Files

| File Nome | Descrizione |

| superiore. SV | Il livello più alto file contiene l'implementazione piatta del progetto. Questo modulo crea un'istanza della sottopartizione flashing_led e del modulo top_counter. |

| top_counter.sv | Contatore a 32 bit di livello superiore che controlla direttamente il LED[1]. L'uscita registrata del contatore controlla il LED[0] e alimenta anche il LED[2] e il LED[3] tramite il modulo blinking_led. |

| led_lampeggiante.sdc | Definisce i vincoli temporali per il progetto. |

| continua… | |

| File Nome | Descrizione |

| led_lampeggiante.SV | In questo tutorial, convertirai questo modulo in una partizione PR principale. Il modulo riceve l'uscita registrata del modulo top_counter, che controlla LED[2] e LED[3]. |

| led_lampeggiante.qpf | Progetto Intel Quartus Prime file contenente l'elenco di tutte le revisioni del progetto. |

| led_lampeggiante.qsf | Impostazioni Intel Quartus Prime file contenente le assegnazioni e le impostazioni per il progetto. |

Nota: La cartella hpr contiene il set completo di files che crei utilizzando questa nota applicativa. Fai riferimento a questi files in qualsiasi momento durante la procedura dettagliata.

Figura 2. Progetto di riferimento Files

Procedura dettagliata del progetto di riferimento

I passaggi seguenti descrivono l'applicazione della riconfigurazione parziale a una progettazione piatta. Il tutorial utilizza il software Intel Quartus Prime Pro Edition per la scheda di sviluppo SoC Intel Arria 10:

- Fase 1: Per iniziare a pagina 6

- Fase 2: Creare un sottomodulo di livello figlio a pagina 6

- Fase 3: Creazione di partizioni di progettazione a pagina 7

- Fase 4: Assegnazione della regione di posizionamento e instradamento per le partizioni PR a pagina 9

- Fase 5: Aggiunta del core IP del controller di riconfigurazione parziale Intel Arria 10 a pagina 10

- Fase 6: Definire le Persona a pagina 13

- Fase 7: Creazione di revisioni a pagina 15

- Fase 8: Generazione dello script del flusso di riconfigurazione parziale gerarchica a pagina 20

- Fase 9: Esecuzione dello script del flusso di riconfigurazione parziale gerarchica a pagina 21

- Fase 10: Programmazione della scheda a pagina 22

Fase 1: Iniziare

Per copiare il progetto di riferimento files al tuo ambiente di lavoro e compila il design piatto lampeggiante_led:

- Crea una directory nel tuo ambiente di lavoro, a10_soc_devkit_blinking_led_hpr.

- Copia la sottocartella tutorials/a10_soc_devkit_blinking_led_hpr/flat scaricata nella directory a10_soc_devkit_blinking_led_hpr.

- Nel software Intel Quartus Prime Pro Edition, fare clic su File ➤ Apri Project e seleziona blinking_led.qpf.

- Per compilare il progetto piatto, fare clic su Elaborazione ➤ Avvia compilazione.

Passaggio 2: creazione di un sottomodulo di livello figlio

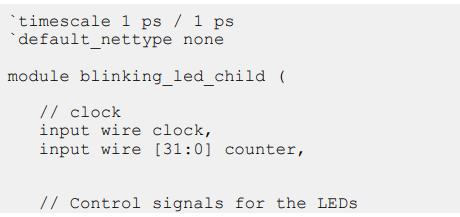

Per convertire questo design piatto in un design PR gerarchico, è necessario creare un sottomodulo figlio (blinking_led_child. SV) nidificato all'interno del sottomodulo padre (blinking_led.sv).

- Crea un nuovo design file, lampeggiante_led_child.sv e aggiungi le seguenti righe di codice a questo file: scala temporale 1 ps / 1 ps `default_nettype none modulo lampeggiante_led_child ( // orologio filo di ingresso orologio, filo di ingresso [31:0] contatore, // segnali di controllo per i LED

- Modifica il flashing_led.sv file per connettere led_two_on al bit 23 del contatore dalla regione statica e istanziare il modulo flashing_led_child. Dopo le modifiche, il tuo flashing_led.sv file deve apparire come segue:

- Modificando tutto il design files, ricompilare il progetto facendo clic su Elaborazione ➤ Avvia compilazione

Passaggio 3: creazione di partizioni di progettazione

È necessario creare partizioni di progettazione per ciascuna regione PR che si desidera riconfigurare parzialmente. Puoi creare un numero qualsiasi di partizioni indipendenti o regioni PR nel tuo progetto. Questo tutorial crea due partizioni di progettazione per le istanze u_blinking_led_child e u_blinking_led.

Per creare partizioni di progettazione per la riconfigurazione parziale gerarchica:

- Fare clic con il pulsante destro del mouse sull'istanza u_blinking_led_child nel Navigatore progetto e fare clic su Partizione di progettazione ➤ Imposta come partizione di progettazione. Accanto a ciascuna istanza impostata come partizione viene visualizzata un'icona di partizione di progettazione.

Figura 3. Creazione di partizioni di progettazione da Project Navigator

- Per definire il tipo di partizione, fare clic con il pulsante destro del mouse sull'istanza u_blinking_led_child nella scheda Gerarchia, fare clic su Progetta partizione ➤ Riconfigurabile. È possibile definire il Tipo di partizione solo dopo aver impostato l'istanza come partizione. La partizione del progetto viene visualizzata nelle assegnazioni View scheda della finestra Partizioni di progettazione.

Figura 4. Finestra Progetta partizioni

- Modificare il nome della partizione nella finestra Progetta partizioni facendo doppio clic sul nome. Per questo progetto di riferimento, rinominare il nome della partizione in pr_partition.

Nota: Quando si crea una partizione, il software Intel Quartus Prime genera automaticamente un nome di partizione, basato sul nome dell'istanza e sul percorso della gerarchia. Questo nome di partizione predefinito può variare a seconda dell'istanza. - Ripeti i passaggi 1 e 2 per assegnare partizioni di progettazione riconfigurabili all'istanza u_blinking_led. Rinominare questa partizione in pr_parent_partition.

Verifica che il file flashing_led.qsf contenga le seguenti assegnazioni, corrispondenti alle partizioni di progettazione riconfigurabili:

Creare partizioni di progettazione per la riconfigurazione parziale

Fase 4: Assegnazione della regione di posizionamento e instradamento per le partizioni PR

Quando crei la revisione di base, il flusso di progettazione PR utilizza l'allocazione della regione di partizione PR per posizionare il nucleo Persona corrispondente nella regione riservata. Per individuare e assegnare la regione PR nella planimetria del dispositivo per la revisione di base:

- Fare clic con il pulsante destro del mouse sull'istanza u_blinking_led_child nel Navigatore progetto e fare clic su Regione di blocco logico ➤ Crea nuova regione di blocco logico. La regione viene visualizzata nella finestra delle regioni di Logic Lock.

- La tua regione di posizionamento deve racchiudere la logica flashing_led_child. Seleziona la regione di posizionamento individuando il nodo in Chip Planner. Fare clic con il pulsante destro del mouse sul nome della regione u_blinking_led_child nel Navigatore progetto e fare clic su Individua nodo ➤ Individua in Chip Planner.

Figura 5. Posizione del nodo Chip Planner per blinking_led

- Nella finestra Logic Lock Regions, specificare le coordinate della regione di posizionamento nella colonna Origin. L'origine corrisponde all'angolo inferiore sinistro della regione. Per esample, per impostare una regione di posizionamento con coordinate (X1 Y1) come (69 10), specificare l'origine come X69_Y10. Il software Intel Quartus Prime calcola automaticamente le coordinate (X2 Y2) (in alto a destra) per la regione di posizionamento, in base all'altezza e alla larghezza specificate.

Nota: Questo tutorial utilizza le coordinate (X1 Y1) – (69 10) e un'altezza e una larghezza pari a 20 per la regione di posizionamento. Definire qualsiasi valore per la regione di posizionamento, a condizione che la regione copra la logica flashing_led_child. - Abilita le opzioni Riservato e Solo core.

- Fare doppio clic sull'opzione Regione di instradamento. Viene visualizzata la finestra di dialogo Logic Lock Routing Region Settings.

- Selezionare Fisso con espansione per il tipo di percorso. La selezione di questa opzione assegna automaticamente una lunghezza di espansione pari a 1.

Nota: La regione di instradamento deve essere più grande della regione di posizionamento, per fornire ulteriore flessibilità all'installatore quando il motore instrada persone diverse. - Ripeti i passaggi da 1 a 6 per l'istanza u_blinking_led. Il posizionamento a livello genitore Ripeti i passaggi da 1 a 6 per l'istanza u_blinking_led. La regione di posizionamento a livello padre deve racchiudere completamente le corrispondenti regioni di posizionamento e instradamento a livello figlio, consentendo allo stesso tempo spazio sufficiente per il posizionamento logico a livello padre. Questo tutorial utilizza le coordinate (X1 Y1) – (66 7), un'altezza di 47 e una larghezza di 26 per la regione di posizionamento dell'istanza u_blinking_led.

Figura 6. Finestra delle regioni di blocco logico

Verifica che il file blinking_led.qsf contenga le seguenti assegnazioni, corrispondenti alla tua planimetria:

- Pianta il progetto di riconfigurazione parziale

- Implementazione incrementale della riconfigurazione parziale

Passaggio 5: aggiunta del core IP del controller di riconfigurazione parziale Intel Arria 10

- Utilizzare il core IP del controller di riconfigurazione parziale Intel Arria 10 per riconfigurare la partizione PR. Questo core IP utilizza JTAG per riconfigurare la partizione PR. Per aggiungere il core IP del controller di riconfigurazione parziale Intel Arria 10 al progetto Intel Quartus Prime:

- Digitare Riconfigurazione parziale nel catalogo IP.

- Per avviare la finestra IP Parametro Editor Pro, selezionare il core IP del controller di riconfigurazione parziale Intel Arria 10 dalla libreria IP e fare clic su Aggiungi.

- Nella finestra di dialogo Nuova variante IP, digitare pr_ip come file file nome e fare clic su Crea. Utilizzare la parametrizzazione predefinita per pr_ip. Assicurarsi che Abilita JTAG la modalità debug e le opzioni Abilita interfaccia bloccata sono attivate e l'opzione Abilita interfaccia slave Avalon-MM è disattivata.

Figura 7. Parametri principali IP del controller di riconfigurazione parziale Intel Arria 10

- Fare clic su Fine e uscire dall'editor dei parametri senza generare il sistema. Il software Intel Quartus Prime crea la variante IP pr_ip.ip file, e aggiunge il file al progetto blinking_led.

Nota:

- Se stai copiando il file pr_ip.ip file dalla cartella hpr, modificare manualmente il file flashing_led.qsf file per includere la seguente riga: set_global_assignment -name IP_FILE pr_ip.ip

- Posiziona l'IP_FILE incarico dopo la DSC_FILE incarichi (jtag.sdc e lampeggiante_led.sdc) nel tuo lampeggiante_led.qsf file. Questo ordinamento garantisce un'adeguata limitazione del nucleo IP di riconfigurazione parziale.

Nota: Per rilevare gli orologi, la DSC file per l'IP PR deve seguire qualsiasi DSC che crea gli orologi utilizzati dal core IP. Faciliti questo ordine assicurando che l'.ip file per il core IP PR viene dopo qualsiasi .ip files o DSC fileViene utilizzato per creare questi orologi nel QSF file per la revisione del progetto Intel Quartus Prime. Per ulteriori informazioni, fare riferimento alla sezione Vincoli temporali nella Guida utente di riconfigurazione parziale IP Core.

Informazioni correlate

- Guida per l'utente delle soluzioni IP per la riconfigurazione parziale

- Per informazioni sul core IP del controller della regione di riconfigurazione parziale.

- Guida per l'utente di riconfigurazione parziale IP Core

- Per informazioni sui vincoli temporali.

Aggiornamento del design di primo livello

Per aggiornare il top.SV file con l'istanza PR_IP:

- Per aggiungere l'istanza PR_IP alla progettazione di livello superiore, decommenta il seguente blocco di codice in top.SV file:

- Per forzare le porte di uscita su 1 logico durante la riconfigurazione, utilizzare l'uscita del segnale di controllo del congelamento da PR_IP. Tuttavia, per osservare che il LED continua a lampeggiare dalla partizione PR genitore mentre PR programma la partizione figlio, il segnale di controllo blocco non spegne il led_two_on. Assicurarsi che pr_led_two_on sia direttamente

- Per assegnare un'istanza della persona principale predefinita (blinking_led), aggiorna top.SV file con il seguente blocco di codice:

Figura 8. Riconfigurazione parziale integrazione IP Core

Passaggio 6: definizione delle persone

Questo progetto di riferimento definisce cinque personalità separate per le partizioni PR padre e figlio. Per definire e includere le personas nel tuo progetto:

- Crea quattro SystemVerilog files, lampeggiante_led_child.sv, lampeggiante_led_child_slow.sv, lampeggiante_led_child_empty.sv e lampeggiante_led_slow.sv nella directory di lavoro per le cinque personas.

Nota: Se crei SystemVerilog files dall'editor di testo Intel Quartus Prime, disabilitare Aggiungi file all'opzione del progetto corrente, quando si salva il file files.

Tabella 2. Personas del progetto di riferimento

| File Nome | Descrizione | Codice |

| lampeggiante_led_child.sv | Persona predefinita per la progettazione a livello figlio |

`scala temporale 1 ps / 1 ps `default_nettype nessuno modulo lampeggiante_led_child ( // orologio orologio a filo in ingresso, contatore del filo di ingresso [31:0],

// Segnali di controllo per il filo di uscita dei LED led_tre_on

); localparam COUNTER_TAP = 23; reg led_tre_on_r;

assegna led_tre_acceso = led_tre_acceso_r; sempre_ff @(orologio posedge) inizio led_tre_on_r <= contatore[COUNTER_TAP]; FINE

modulo finale |

| continua… | ||

| File Nome | Descrizione | Codice |

| lampeggiante_led_child_slow.sv | IL

LED_TRE lampeggia più lentamente |

`scala temporale 1 ps / 1 ps `default_nettype nessuno

modulo lampeggiante_led_bambino_lento (

// orologio orologio a filo in ingresso, contatore del filo di ingresso [31:0],

// Segnali di controllo per il filo di uscita dei LED led_tre_on );

localparam COUNTER_TAP = 27; reg led_tre_on_r;

assegna led_tre_acceso = led_tre_acceso_r; sempre_ff @(orologio posedge) inizio led_tre_on_r <= contatore[COUNTER_TAP]; FINE

modulo finale |

| lampeggiante_led_child_empty.sv | IL

LED_TRE rimane acceso |

`scala temporale 1 ps / 1 ps `default_nettype nessuno

modulo lampeggiante_led_bambino_vuoto (

// orologio orologio a filo in ingresso, contatore del filo di ingresso [31:0],

// Segnali di controllo per il filo di uscita dei LED led_tre_on

);

// Il LED è attivo basso assegna led_three_on = 1'b0;

modulo finale |

| led_lampeggiante_lento.sv | Il LED_TWO

lampeggia più lentamente. |

`scala temporale 1 ps / 1 ps `default_nettype nessuno modulo lampeggiante_led_lento( // orologio orologio a filo in ingresso, contatore del filo di ingresso [31:0],

// Segnali di controllo per il cavo di uscita dei LED led_two_on, filo di uscita led_tre_acceso

);

localparam COUNTER_TAP = 27; reg led_two_on_r; assegna led_two_on = led_two_on_r;

// Il contatore: sempre_ff @(orologioposedge) inizio led_due_on_r <= contatore[COUNTER_TAP]; FINE

lampeggiante_led_bambino u_lampeggiante_led_bambino( .led_tre_accesi (led_tre_accesi), .contatore (contatore), .clock (orologio) |

| File Nome | Descrizione | Codice |

| );ndmodulo |

Passaggio 3: creazione di partizioni di progettazione a pagina 7

Passaggio 7: creazione di revisioni

Il flusso di progettazione PR utilizza la funzionalità di revisione del progetto nel software Intel Quartus Prime. Il progetto iniziale è la revisione di base, in cui definisci i confini della regione statica e le regioni riconfigurabili sull'FPGA. Dalla revisione di base si creano più revisioni. Queste revisioni contengono le diverse implementazioni per le regioni PR. Tuttavia, tutte le revisioni dell'implementazione PR utilizzano gli stessi risultati di posizionamento e instradamento di livello superiore della revisione di base. Per compilare un progetto PR, è necessario creare una revisione dell'implementazione PR e una revisione della sintesi per ciascun personaggio. In questo progetto di riferimento, oltre alla revisione di base (blinking_led), i tre personaggi a livello di bambino e i due personaggi a livello di genitore contengono cinque revisioni di sintesi separate e cinque revisioni di implementazione separate:

Tabella 3. Revisioni per le categorie “due genitori” e “tre figli”.

| Revisione della sintesi | Revisione dell'implementazione |

| lampeggiante_led_parent, lampeggiante_led_default | lampeggiante_led_pr_alfa |

| lampeggiante_led_parent, lampeggiante_led_child_lento | lampeggiante_led_pr_bravo |

| lampeggiante_led_parent, lampeggiante_led_child_empty | lampeggiante_led_pr_charlie |

| lampeggiante_led_genitore_lento, lampeggiante_led_bambino_lento | lampeggiante_led_pr_delta |

| lampeggiante_led_parent_slow, lampeggiante_led_child_empty | lampeggiante_led_pr_emma |

Creazione di revisioni di implementazione

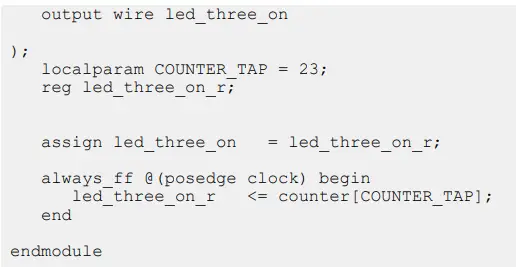

Per creare le revisioni dell'implementazione PR:

- Per aprire la finestra di dialogo Revisioni, fare clic su Progetto ➤ Revisioni.

- Per creare una nuova revisione, fare doppio clic su < >.

- Specificare il nome della revisione come lampeggiante_led_pr_alpha e selezionare lampeggiante_led per Basato sulla revisione.

- Disattiva l'opzione Imposta come revisione corrente e fai clic su OK.

- Allo stesso modo, crea le revisioni lampeggiante_led_pr_bravo, lampeggiante_led_pr_charlie, lampeggiante_led_pr_delta e lampeggiante_led_pr_emma, in base alla revisione lampeggiante_led.

Nota: Non impostare le revisioni di cui sopra come revisione corrente.

Figura 9. Creazione di revisioni

Creazione di revisioni di sola sintesi

Per creare revisioni di sola sintesi per le personas, è necessario assegnare l'entità di livello superiore e il corrispondente SystemVerilog file per ciascuno dei personaggi:

- Nel software Intel Quartus Prime, fare clic su Progetto ➤ Revisioni.

- Crea revisione lampeggiante_led_default in base alla revisione lampeggiante_led. Non impostare questa revisione come revisione corrente.

- Modificare il filelinking_led_default.qsf file includere i seguenti incarichi:

set_global_assignment -name TOP_LEVEL_ENTITY lampeggiante_led_child

set_global_assignment -nome SYSTEMVERILOG_FILE - Allo stesso modo, crea revisioni Blinding_led_child_slow, Blinking_led_child_empty, Blinking_led_parent e Blinking_led_parent_slow basate sulla revisione Blinking_led. Non impostare queste revisioni come revisioni correnti.

- Aggiorna lampeggiante_led_child_slow.qsf, lampeggiante_led_child_empty.qsf, lampeggiante_led_parent.qsf e lampeggiante_led_parent_slow.qsf files con il loro corrispondente

TOP_LEVEL_ENTITY e SYSTEMVERILOG_FILE Compiti:

- Per evitare errori di sintesi, assicurarsi che la revisione della sintesi fileI messaggi per le partizioni secondarie non contengono partizioni di progettazione, assegnazioni di pin o blocco logico

incarichi regionali. Inoltre, la revisione della sintesi fileI messaggi per le partizioni principali devono contenere solo assegnazioni di partizioni di progettazione per le partizioni secondarie corrispondenti. Rimuovi queste assegnazioni, se presenti, in flashing_led_default.qsf, lampeggiante_led_child_slow.qsf, lampeggiante_led_child_empty.qsf, lampeggiante_led_parent.qsf e lampeggiante_led_parent_slow.pdf files

- Includere le seguenti assegnazioni in lampeggiante_led_parent.qsf e lampeggiante_led_parent_slow.qsf files:

- Verificare che il flashing_led.qpf file contiene le seguenti revisioni, in nessun ordine particolare:

- Nota: Se stai copiando la revisione files dalla cartella hpr, aggiornare manualmente il file flashing_led.qpf file con le righe di codice sopra.

Specifica del tipo di revisione

È necessario assegnare il tipo di revisione per ciascuna delle tue revisioni. Esistono tre tipi di revisione:

- Riconfigurazione parziale – Base

- Riconfigurazione Parziale – Sintesi della Persona

- Riconfigurazione parziale – Implementazione Persona

- La seguente tabella elenca le assegnazioni del tipo di revisione per ciascuna revisione:

Tabella 4. Tipi di revisione

| Nome revisione | Tipo di revisione |

| led_lampeggiante.qsf | Riconfigurazione parziale – Base |

| led_lampeggiante_default.qsf | Riconfigurazione Parziale – Sintesi della Persona |

| lampeggiante_led_child_empty.qsf | Riconfigurazione Parziale – Sintesi della Persona |

| lampeggiante_led_child_slow.qsf | Riconfigurazione Parziale – Sintesi della Persona |

| lampeggiante_led_parent.qsf | Riconfigurazione Parziale – Sintesi della Persona |

| lampeggiante_led_parent_slow.qsf | Riconfigurazione Parziale – Sintesi della Persona |

| lampeggiante_led_pr_alpha.qsf | Riconfigurazione parziale – Implementazione Persona |

| lampeggiante_led_pr_bravo.qsf | Riconfigurazione parziale – Implementazione Persona |

| lampeggiante_led_pr_charlie.qsf | Riconfigurazione parziale – Implementazione Persona |

| lampeggiante_led_pr_delta.qsf | Riconfigurazione parziale – Implementazione Persona |

| lampeggiante_led_pr_emma.qsf | Riconfigurazione parziale – Implementazione Persona |

- Fare clic su Progetto ➤ Revisioni. Viene visualizzata la finestra di dialogo Revisioni.

- Selezionare lampeggiante_led nella colonna Nome revisione e fare clic su Imposta corrente.

- Fare clic su Applica. Si apre la revisione lampeggiante_led.

- Per impostare il tipo di revisione per lampeggiante_led, fare clic su Assegnazioni ➤ Impostazioni ➤ Generale.

- Selezionare il tipo di revisione come Riconfigurazione parziale – Base.

- Allo stesso modo, imposta i tipi di revisione per le altre dieci revisioni, come elencato nella tabella sopra.

- Nota: È necessario impostare ciascuna revisione come revisione corrente prima di assegnare il tipo di revisione. Verificare che ogni file .qsf file contiene il seguente compito:

- Nota: Aggiungi eventuali impostazioni specifiche dell'Fitter che desideri utilizzare nella compilazione dell'implementazione PR alle revisioni dell'implementazione della persona. Le impostazioni specifiche dell'Fitter influiscono sull'adattamento della persona, ma non influiscono sulla regione statica importata. Puoi anche aggiungere qualsiasi impostazione specifica della sintesi alle revisioni della sintesi personale individuale.

Crea revisioni per le persone

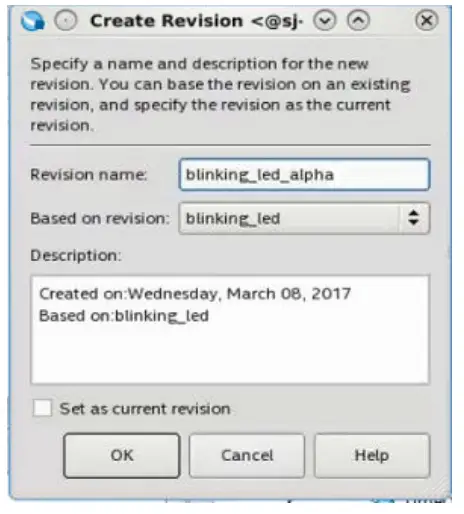

Fase 8: Generazione dello script del flusso di riconfigurazione parziale gerarchica

Per generare lo script del flusso di riconfigurazione parziale gerarchica:

- Dalla shell dei comandi di Intel Quartus Prime, crea un modello di flusso eseguendo il comando seguente:

- Intel Quartus Prime genera a10_hier_partial_reconfig/flow.tcl file.

- Rinominare il file generato a10_hier_partial_reconfig/setup.tcl.example in a10_hier_partial_reconfig/setup.tcl e modificare lo script per specificare i dettagli del progetto di riconfigurazione parziale:

a. Per definire il nome del progetto, aggiornare la seguente riga: b. Per definire la revisione di base, aggiornare la seguente riga:

b. Per definire la revisione di base, aggiornare la seguente riga:

- Per definire ciascuna delle revisioni di implementazione della riconfigurazione parziale, insieme ai nomi delle partizioni PR e alla revisione di origine che implementa le revisioni, aggiornare le seguenti righe:

Nota: Tutti i progetti di revisione devono trovarsi nella stessa directory di flashing_led.qpf. Altrimenti, aggiorna lo script del flusso di conseguenza.

Fase 9: Esecuzione dello script del flusso di riconfigurazione parziale gerarchica

Per eseguire lo script del flusso di riconfigurazione parziale gerarchica:

- Fare clic su Strumenti ➤ Script Tcl. Viene visualizzata la finestra di dialogo Script Tcl.

- Fare clic su Aggiungi al progetto, sfogliare e selezionare a10_hier_partial_reconfig/flow.tcl.

- Selezionare a10_hier_partial_reconfig/flow.tcl nel riquadro Librerie e fare clic su Esegui.

Questo script esegue la sintesi per le tre personalità. Intel Quartus Prime genera un oggetto SRAM File (.sof), un oggetto SRAM parzialmente mascherato File (.pmsf) e un file binario non elaborato File (.rbf) per ciascuna delle personas.

Nota: per eseguire lo script dalla shell dei comandi di Intel Quartus Prime, digitare il comando seguente:

- Compilare il progetto di riconfigurazione parziale

- Utilizzo dello script del flusso di riconfigurazione parziale

- Configurazione dello script del flusso di riconfigurazione parziale

- Genera programmazione Files

Fase 10: Programmazione della scheda

Prima di iniziare:

- Collega l'alimentatore alla scheda di sviluppo SoC Intel Arria 10.

- Collega il cavo USB Blaster alla porta USB del tuo PC e alla porta USB Blaster sulla scheda di sviluppo.

Per eseguire la progettazione sulla scheda di sviluppo SoC Intel Arria 10:

- Aprire il software Intel Quartus Prime e fare clic su Strumenti ➤ Programmatore.

- Nel Programmatore, fare clic su Hardware Setup e selezionare USB-Blaster.

- Fare clic su Rilevamento automatico e selezionare il dispositivo, 10AS066N3.

- Fare clic su OK. Il software Intel Quartus Prime rileva e aggiorna il programmatore con i tre chip FPGA sulla scheda.

- Selezionare il dispositivo 10AS066N3, fare clic su Cambia File e caricare il file flashing_led_pr_alpha.sof file.

- Abilita Programma/Configura per flashing_led_pr_alpha.sof file.

- Fai clic su Avvia e attendi che la barra di avanzamento raggiunga il 100%.

- Osserva i LED sulla scheda che lampeggiano alla stessa frequenza del design piatto originale.

- Per programmare solo la regione PR secondaria, fare clic con il pulsante destro del mouse su flashing_led_pr_alpha.sof file nel Programmatore e fare clic su Aggiungi Programmazione PR File.

- Selezionare il lampeggiante_led_pr_bravo.pr_parent_partition.pr_partition.rbf file.

- Disabilita Programma/Configura per flashing_led_pr_alpha.sof file.

- Abilita Programma/Configura per flashing_led_pr_bravo.pr_parent_partition.pr_partition.rbf file e fare clic su Avvia. Sulla scheda osservare il LED[0] e il LED[1] che continuano a lampeggiare. Quando la barra di avanzamento raggiunge il 100%, il LED[2] lampeggia alla stessa velocità e il LED[3] lampeggia più lentamente.

- Per programmare sia la regione PR genitore che quella figlio, fare clic con il pulsante destro del mouse su .rbf file nel programmatore e fare clic su Cambia programmazione PR File.

- Selezionare il lampeggiante_led_pr_delta.pr_parent_partition.rbf file.

- Fare clic su Avvia. Sulla scheda osservare che il LED[0] e il LED[1] continuano a lampeggiare. Quando la barra di avanzamento raggiunge il 100%, sia il LED[2] che il LED[3] lampeggiano più lentamente.

- Ripetere i passaggi precedenti per riprogrammare dinamicamente solo la regione PR secondaria o entrambe le regioni PR genitore e figlio contemporaneamente.

Figura 10. Programmazione della scheda di sviluppo SoC Intel Arria 10

Modifica di una persona esistente

- Puoi modificare una persona esistente, anche dopo aver compilato completamente la revisione di base.

- Per esempioample, per far sì che la persona flashing_led_child_slow lampeggi ancora più lentamente:

- Nel flashing_led_child_slow.sv file, modificare il parametro COUNTER_TAP da 27 a 28.

- Per risintetizzare e reimplementare questa persona, è necessario ricompilare tutte le revisioni di sola sintesi e le revisioni di implementazione interessate dalla modifica. Modificare lo script setup.tcl per includere le seguenti righe:

Nota: Quando definisci pr_parent_parition per la revisione flashing_led_pr_delta, importi lo snapshot finale di quella persona per l'implementazione. Di conseguenza, l'implementazione della logica della partizione padre rimane la stessa, pur modificando e implementando la partizione figlio corrispondente.

Nota: Quando definisci pr_parent_parition per la revisione flashing_led_pr_delta, importi lo snapshot finale di quella persona per l'implementazione. Di conseguenza, l'implementazione della logica della partizione padre rimane la stessa, pur modificando e implementando la partizione figlio corrispondente. Questo comando risintetizza la revisione della sintesi flashing_led_child_slow e quindi esegue la compilazione dell'implementazione PR utilizzando flashing_led_pr_bravo.

Questo comando risintetizza la revisione della sintesi flashing_led_child_slow e quindi esegue la compilazione dell'implementazione PR utilizzando flashing_led_pr_bravo. - Per eseguire la compilazione delle revisioni di sola sintesi, eseguire il seguente comando: Questo comando non ricompila la revisione di base.

- Per eseguire la compilazione delle revisioni dell'implementazione, eseguire il comando seguente:

- Questo comando non ricompila la revisione di base.

- Seguire i passaggi nella Fase 10: Programmazione della scheda a pagina 22 per programmare l'RBF risultante file nell'FPGA.

Nota: Per evitare di eseguire l'intero flusso per ogni revisione, definire le revisioni di sola sintesi e le revisioni di implementazione nello script setup.tcl ed eseguire lo script.

Aggiunta di una nuova persona al design

Dopo aver compilato completamente le revisioni di base, puoi ancora aggiungere nuovi personaggi e compilare individualmente questi personaggi.

Per esempioample, per definire una nuova personalità bambino per flashing_led_parent_slow, che spegne led_tre:

- Copia lampeggiante_led_child_empty.sv in lampeggiante_led_chdild_off.sv.

- Nel file flashing_led_child_off.sv file, modifica l'assegnazione, assegna led_tre_on = 1'b0; per assegnare led_tre_accesi = 1'b1;. Assicurati di modificare il nome del modulo da lampeggiante_led_child_empty a lampeggiante_led_child_off.

- Creare una nuova revisione di sintesi, lampeggiante_led_child_off, seguendo i passaggi in Creazione di revisioni di sola sintesi a pagina 16.

Nota: La revisione flashing_led_child_off deve utilizzare il file flashing_led_child_off.sv file. - Creare una nuova revisione dell'implementazione, lampeggiante_led_pr_foxtrot, seguendo i passaggi in Creazione delle revisioni dell'implementazione a pagina 15.

- Aggiorna a10_hier_partial_reconfig/setup.tcl file per definire la nuova implementazione delle PR:

- Compila solo questa nuova sintesi e revisione dell'implementazione eseguendo il seguente comando:

Per informazioni complete sulla riconfigurazione parziale gerarchica per i dispositivi Intel Arria 10, fare riferimento a Creazione di un progetto di riconfigurazione parziale nel volume 1 del manuale Intel Quartus Prime Pro Edition.

Informazioni correlate

- Creazione di un progetto di riconfigurazione parziale

- Formazione online sulla riconfigurazione parziale

Cronologia delle revisioni del documento

Tabella 5. Cronologia delle revisioni del documento

| Versione del documento | Software Version | Cambiamenti |

| 2017.11.06 | 17.1.0 | • Aggiornato il Requisiti di progettazione di riferimento sezione con la versione del software

• Aggiornato il Progetto di riferimento piatto senza partizionamento PR figura con modifiche al blocco di progettazione • Aggiornato il Progetto di riferimento Files tabella con le informazioni sul Modulo Top_counter.sv • Aggiornato il Riconfigurazione parziale Integrazione IP Core figura con modifiche al blocco di progettazione • Aggiornati i dati – Finestra Partizioni di progettazione E Finestra Regioni blocco logico per riflettere la nuova GUI • File cambiamenti di nome • Modifiche al testo |

| 2017.05.08 | 17.0.0 | Il rilascio iniziale del documento |

Documenti / Risorse

|

Intel AN 805 Riconfigurazione parziale gerarchica di un progetto sulla scheda di sviluppo SoC Arria 10 [pdf] Guida utente AN 805 Riconfigurazione parziale gerarchica di un progetto sulla scheda di sviluppo SoC Arria 10, AN 805, Riconfigurazione parziale gerarchica di un progetto sulla scheda di sviluppo SoC Arria 10, Riconfigurazione di un progetto sulla scheda di sviluppo SoC Arria 10, Scheda di sviluppo SoC Arria 10, SoC 10 Consiglio di sviluppo |