Compilatore di sintesi Intel di alto livello Pro Edition

Informazioni sul prodotto

| Nome del prodotto | Compilatore di sintesi Intel di alto livello Pro Edition |

|---|---|

| Versione | 22.4 |

| Data di rilascio | 19 dicembre 2022 |

| Avviso di deprecazione | Si prevede che lo sarà il compilatore di sintesi di alto livello Intel deprecato dopo la versione 23.4. |

Istruzioni per l'uso del prodotto

Guida introduttiva

- Inizializza l'ambiente del compilatore.

- Review i vari design esample ed esercitazioni forniti con il compilatore Intel HLS.

Guida per l'utente

- La Guida per l'utente fornisce istruzioni su

- Sintetizzazione, verifica e simulazione della proprietà intellettuale (IP) progettata per i prodotti Intel FPGA.

- Passando attraverso l'intero flusso di sviluppo del tuo componente, dalla creazione del componente e del banco di prova fino all'integrazione dell'IP del componente in un sistema più grande con il software Intel Quartus Prime.

Guida alle migliori pratiche

La Guida alle migliori pratiche fornisce tecniche e pratiche che è possibile applicare per migliorare l'utilizzo dell'area FPGA e le prestazioni del componente HLS. Applica queste best practice dopo aver verificato la correttezza funzionale del tuo componente.

Manuale di riferimento

Il Manuale di riferimento fornisce informazioni di riferimento sulle funzionalità supportate dal compilatore Intel HLS. Trova i dettagli sulle opzioni dei comandi del compilatore Intel HLS, intestazione files, pragma, attributi, macro, dichiarazioni, argomenti e librerie di modelli.

Note sulla versione di Intel® High Level Synthesis Compiler Pro Edition versione 22.4

- Le note sulla versione di Intel® High Level Synthesis Compiler Pro Edition forniscono informazioni aggiornate su Intel High Level Synthesis Compiler Pro Edition versione 22.4.

In attesa di deprecazione del compilatore Intel HLS

- Per mantenere l'accesso alle più recenti funzionalità di progettazione di alto livello FPGA, ottimizzazioni e utilità di sviluppo, migrate i vostri progetti esistenti per utilizzare Intel oneAPI Base Toolkit.

- Il compilatore Intel High Level Synthesis (HLS) dovrebbe essere deprecato dopo la versione 23.4.

- Visita la pagina del prodotto Intel oneAPI per consigli sulla migrazione o visita il forum della community Intel High Level Design per qualsiasi domanda o richiesta.

Informazioni sulla libreria della documentazione di Intel HLS Compiler Pro Edition

- La documentazione per Intel HLS Compiler Pro Edition è suddivisa in alcune pubblicazioni. Utilizzare la tabella seguente per trovare la pubblicazione che contiene le informazioni di Intel HLS Compiler Pro Edition che si sta cercando:

Tabella 1. Libreria di documentazione del compilatore di sintesi Intel High-Level Pro Edition

| Titolo e descrizione | |

| Note di rilascio

Fornisce informazioni aggiornate sul compilatore Intel HLS. |

Collegamento |

| Guida introduttiva

Diventa subito operativo con il compilatore Intel HLS imparando come inizializzare l'ambiente del compilatore e riviewing i vari design esample ed esercitazioni forniti con il compilatore Intel HLS. |

Collegamento |

| Guida per l'utente

Fornisce istruzioni sulla sintesi, verifica e simulazione della proprietà intellettuale (IP) progettata per i prodotti Intel FPGA. Segui l'intero flusso di sviluppo del tuo componente, dalla creazione del componente e del banco di prova fino all'integrazione dell'IP del componente in un sistema più grande con il software Intel Quartus Prime. |

Collegamento |

| Guida alle migliori pratiche

Fornisce tecniche e pratiche che è possibile applicare per migliorare l'utilizzo dell'area FPGA e le prestazioni del componente HLS. In genere, queste procedure consigliate vengono applicate dopo aver verificato la correttezza funzionale del componente. |

Collegamento |

| Manuale di riferimento

Fornisce informazioni di riferimento sulle funzionalità supportate dal compilatore Intel HLS. Trova i dettagli sulle opzioni dei comandi del compilatore Intel HLS, intestazione files, pragma, attributi, macro, dichiarazioni, argomenti e librerie di modelli. |

Collegamento |

Società Intel. Tutti i diritti riservati. Intel, il logo Intel e altri marchi Intel sono marchi di Intel Corporation o delle sue consociate. Intel garantisce le prestazioni dei suoi prodotti FPGA e semiconduttori in base alle specifiche correnti in conformità con la garanzia standard di Intel, ma si riserva il diritto di apportare modifiche a qualsiasi prodotto e servizio in qualsiasi momento senza preavviso. Intel non si assume alcuna responsabilità derivante dall'applicazione o dall'uso di informazioni, prodotti o servizi qui descritti, salvo quanto espressamente concordato per iscritto da Intel. Si consiglia ai clienti Intel di ottenere la versione più recente delle specifiche del dispositivo prima di fare affidamento su qualsiasi informazione pubblicata e prima di effettuare ordini per prodotti o servizi.

*Altri nomi e marchi potrebbero essere rivendicati come proprietà di terzi.

In attesa di deprecazione del compilatore Intel HLS

- Per mantenere l'accesso alle più recenti funzionalità di progettazione di alto livello FPGA, ottimizzazioni e utilità di sviluppo, migrate i vostri progetti esistenti per utilizzare Intel oneAPI Base Toolkit.

- Il compilatore Intel High Level Synthesis (HLS) dovrebbe essere deprecato dopo la versione 23.4.

- Visita la pagina del prodotto Intel oneAPI per consigli sulla migrazione o visita il forum della community Intel High Level Design per qualsiasi domanda o richiesta.

Nuove funzionalità e miglioramenti

- Intel High Level Synthesis Compiler Pro Edition versione 22.4 include le seguenti nuove funzionalità:

- Rilascio di manutenzione.

- Nessuna nuova funzionalità o miglioramento per Intel HLS Compiler Pro Edition versione 22.4.

Cambiamenti nel comportamento del software

- Questa sezione documenta le istanze in cui le funzionalità di Intel HLS Compiler Pro Edition versione 22.4 sono state modificate rispetto alle versioni precedenti del compilatore.

Rilascio di manutenzione.

- Nessuna modifica nel comportamento del software per Intel HLS Compiler Pro Edition versione 22.4.

Prerequisiti Intel Synthesis Compiler Pro Edition

- Intel HLS Compiler Pro Edition fa parte di Intel Quartus® Prime Pro Edition Design Suite. È possibile installare il compilatore Intel HLS come parte dell'installazione del software Intel Quartus Prime o installarlo separatamente. Richiede Intel Quartus Prime e software aggiuntivo da utilizzare.

- Per istruzioni dettagliate sull'installazione del software Intel Quartus Prime Pro Edition, inclusi requisiti di sistema, prerequisiti e requisiti di licenza, vedere installazione e licenza del software Intel FPGA.

- Il compilatore Intel HLS richiede il seguente software oltre a Intel Quartus Prime:

Compilatore C++

- Su Linux, Intel HLS Compiler richiede GCC 9.3.0 inclusa la libreria GNU C++ e le utilità binarie (binutils).

- Questa versione di GCC viene fornita come parte dell'installazione del compilatore Intel HLS. Dopo aver installato il compilatore Intel HLS, GCC 9.3.0 è disponibile in /gcc.

- Importante: Il compilatore Intel HLS utilizza il file /gcc come directory della toolchain. Utilizza questa installazione di GCC per tutto il tuo lavoro di progettazione relativo a HLS.

- Per Windows, installare una delle seguenti versioni di Microsoft* Visual Studio* Professional:

- Microsoft Visual Studio 2017 professionale

- Comunità di Microsoft Visual Studio 2017

- Per il supporto C++ 17 più aggiornato, assicurati di usare la versione più recente di Visual Studio 2017.

- Importante: Il software Intel HLS Compiler non supporta versioni di Microsoft Visual Studio diverse da quelle specificate per l'edizione del software.

Software di simulazione Siemens* EDA Questa®

- Sui sistemi Windows e RedHat Linux, è possibile installare il software di simulazione Questa® dal programma di installazione del software Intel Quartus Prime. Le opzioni disponibili sono le seguenti:

- Questa edizione Intel FPGA

- Questa edizione iniziale di Intel FPGA

- Sia Questa Intel FPGA Edition che Questa Intel FPGA Starter Edition richiedono licenze. La licenza per Questa Intel FPGA Starter Edition è gratuita. Per i dettagli, fare riferimento a Installazione e licenza del software Intel FPGA.

- In alternativa, è possibile utilizzare la propria versione con licenza del software Siemens* EDA ModelSim* SE o Siemens EDA Questa Advanced Simulator.

- Sui sistemi Linux, Questa – Intel FPGA Edition e Questa – Intel FPGA Starter Edition richiedono i pacchetti di strumenti di sviluppo Red Hat*.

- Per informazioni su tutte le versioni del software ModelSim e Questa supportate dal software Intel, fare riferimento alla sezione Informazioni sull'interfaccia EDA nelle Note sulla versione del supporto per software e dispositivi per la propria edizione di Intel Quartus Prime Pro Edition.

Informazioni correlate

- Guida introduttiva al compilatore di sintesi Intel di alto livello

- Sistemi operativi supportati

- Requisiti software per l'installazione e la licenza del software Intel FPGA

- Informazioni sull'interfaccia EDA (Intel Quartus Prime Pro Edition)

Problemi noti e soluzioni alternative

- Questa sezione fornisce informazioni sui problemi noti che interessano Intel HLS Compiler Pro Edition versione 22.4.

| Descrizione | Soluzione alternativa |

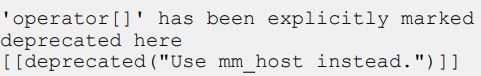

| Quando si utilizza la classe deprecata mm_master, il compilatore emette un messaggio di avviso simile al seguente:

Questo messaggio non indica quale parte del codice deve essere modificata. |

Evitare questo messaggio di avviso utilizzando la classe mm_host, che sostituisce la classe obsoleta mm_master. |

| (Solo Windows) La compilazione di un progetto in una directory con un percorso lungo può causare errori di compilazione.

Controlla il file debug.log file perché “non ho potuto trovare file" errori. Questi errori possono indicare che il percorso è troppo lungo. |

Compilare il progetto in una directory con un percorso breve. |

| (Solo Windows) Un percorso lungo per la directory di installazione di Intel Quartus Prime può impedire la corretta compilazione ed esecuzione dei tutorial del compilatore Intel HLS ed example disegni.

Controlla il file debug.log file perché “non ho potuto trovare file" errori. Questi errori possono indicare che il percorso è troppo lungo. |

Sposta i tutorial ed examples a un nome di percorso breve prima di tentare di eseguirli. |

| Descrizione | Soluzione alternativa |

| Le librerie destinate a OpenCL* e scritte in HLS non possono utilizzare flussi o pipe come interfaccia tra il codice OpenCL e la libreria scritta in HLS.

Tuttavia, la libreria in HLS può utilizzare flussi o pipe se entrambi gli endpoint si trovano all'interno della libreria (ad esample, un flusso che collega due funzioni di attività). |

N / A |

| L'applicazione del parametro ihc::maxburst alle interfacce host Avalon® Memory-Mapped può causare il blocco del progetto nella simulazione. | N / A |

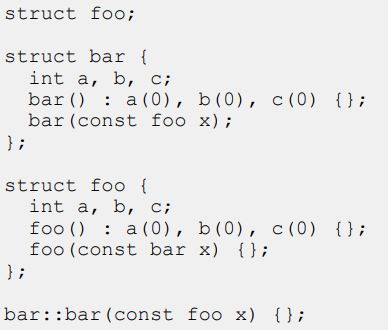

| In alcuni casi non comuni, se si hanno due classi i cui costruttori richiedono ciascuna istanze dell'altra classe come input, il compilatore potrebbe bloccarsi.

Per esempioample, la compilazione del seguente frammento di codice causa l'arresto anomalo del compilatore:

|

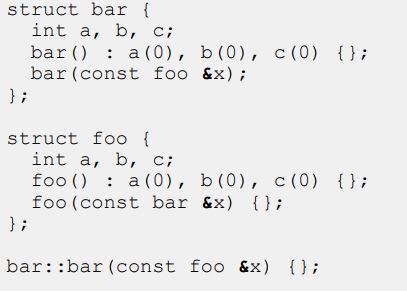

Evitare di creare una definizione circolare. Invece, usa un puntatore o un riferimento nel tuo costruttore di copie.

Per esempioample, trasforma lo snippet di codice precedente nel codice seguente e passa lo struct come riferimento al costruttore:

|

| Le librerie destinate a OpenCL e scritte in HLS potrebbero far sì che i kernel OpenCL che includono la libreria abbiano una compilazione incrementale più conservativa. | N / A |

| Quando si sviluppa una libreria, se si dispone di un #define che definisce un valore da utilizzare successivamente in un #pragma, il comando fpga_crossgen fallisce.

Per esempioample, il seguente codice non può essere compilato da

|

Usa pragma invece di #pragma.

Per esempioample, quanto segue viene compilato correttamente con il file

|

| Quando si utilizza l'opzione di comando -c per avere compilazione e collegamento separatitages nel flusso di lavoro e se non si specifica l'opzione -march nei collegamentitage (o specifica un valore diverso per l'opzione -march), il tuo collegamento stage potrebbe fallire con o senza messaggi di errore. | Assicurarsi di utilizzare lo stesso valore dell'opzione -march per entrambe le compilazioni con l'opzione del comando -c stage e il collegamento stage. |

| Descrizione | Soluzione alternativa |

| L'applicazione dell'attributo di memoria hls_merge a un array dichiarato all'interno di un ciclo srotolato o parzialmente srotolato provoca l'unione delle copie dell'array attraverso le iterazioni del ciclo srotolato.

|

Evitare di utilizzare l'attributo di memoria hls_merge nei loop srotolati.

Se è necessario unire le memorie in un ciclo srotolato, dichiarare esplicitamente un array di tipo struct per l'unione della larghezza o dichiarare un array più profondo per l'unione della profondità.

|

| Nella memoria delle funzioni ViewSecondo il rapporto di progettazione di alto livello, alcuni ricordi con ambito funzionale potrebbero apparire come "ottimizzati". | Nessuno.

Quando un file contiene funzioni che sono componenti e funzioni che non sono componenti, tutte le variabili con ambito funzione sono elencate nel riquadro Elenco memoria funzione, ma solo le variabili dei componenti hanno informazioni su di esse da mostrare nella memoria funzione View riquadro. |

| Alcuni report di progettazione di alto livello non riescono in Microsoft Internet Explorer*. | Utilizza uno dei seguenti browser per view i rapporti:

• Google Chrome* • Microsoft Edge* • Mozilla Firefox* |

| Il Ciclo Viewer nei rapporti di progettazione di alto livello presenta le seguenti restrizioni:

• Il comportamento dei cluster senza stallo non è modellato nel Loop Viewehm. La latenza finale mostrata nel Loop Viewer per un cluster senza stallo è in genere più pessimistico (ovvero più alto) della latenza effettiva del progetto. Per una descrizione del clustering e dei cluster senza stallo, fare riferimento a Clustering del Datapath nel Intel di alto livello Guida alle migliori pratiche del compilatore di sintesi Pro Edition. • Gli stalli dovuti a letture e scritture dalla memoria o alle istruzioni di stampa non vengono modellati. • Conteggi di iterazioni elevati (>1000) causano prestazioni lente del ciclo Vieweh. • Non è possibile specificare un conteggio di iterazioni pari a zero (0) nel Loop Vieweh. |

Nessuno. |

| I collegamenti in alcuni report nei report di progettazione di alto livello generati su sistemi Windows non funzionano. | Genera report di progettazione di alto livello (ovvero compila il codice) su un sistema Linux. |

| Utilizzando una struttura con un singolo tipo di dati ac_int in un'interfaccia di streaming che utilizza i pacchetti (ihc::usesPackets ) non funziona.

Per esempioample, il seguente frammento di codice non funziona:

|

Per utilizzare questa combinazione nel tuo progetto, rispetta le seguenti restrizioni:

• La dimensione dei dati interni ac_int deve essere multipla di 8 • La dichiarazione del tipo di interfaccia del flusso deve specificare ihc::bitsPerSymbol<8> Per esempioample, il seguente frammento di codice funziona:

|

| Descrizione | Soluzione alternativa | |

| Quando si esegue una simulazione ad alto rendimento del componente utilizzando le chiamate della funzione enqueue, se non si utilizza la funzione ihc_hls_component_run_all per eseguire le chiamate del componente accodato dopo tutte le chiamate ihc_hls_enqueue per quel componente, si verificano i seguenti comportamenti:

• In emulazione, vengono eseguite le funzioni dei componenti accodati. • Nella simulazione, le funzioni dei componenti accodati non vengono eseguite e non vengono forniti messaggi di errore o di avviso. |

Assicurarsi di utilizzare la funzione ihc_hls_component_run_all dopo che tutte le chiamate ihc_hls_enqueue per quel componente eseguono le chiamate di funzione del componente accodato. | |

| Avvio di una funzione di attività con ihc::launch_always_run | Per evitare di eliminare l'ottimizzazione, aggiungi un po'(1) | |

| rimuove gli attributi di ottimizzazione applicati all'attività | loop alla funzione interessata applica il controllo corrispondente | |

| funzione. | pragma al ciclo while(1) invece della funzione. | |

| Nel seguente codice example, l'attributo applicato alla funzione viene ignorato. I rapporti di progettazione di alto livello mostrano un II di 1 per questo compito invece del richiesto II di 4. | Il seguente codice esample mostrano come implementare questa modifica per il codice precedente esampon: | |

|

|

|

| Per i progetti Cyclone® V che contengono più componenti HLS, quando utilizzi il comando i++ per compilare il tuo progetto su hardware (i++ -march=CycloneV), potresti ricevere un errore.

Sebbene il testo dell'errore differisca a seconda del progetto, la firma dell'errore è un errore di compilazione di Intel Quartus Prime dovuto a una cattiva sintassi di Verilog. Un modulo tenta di utilizzare una funzione che il compilatore Intel Quartus Prime non riesce a trovare. |

Se riscontri questo problema, inserisci ciascun componente HLS in un progetto separato. | |

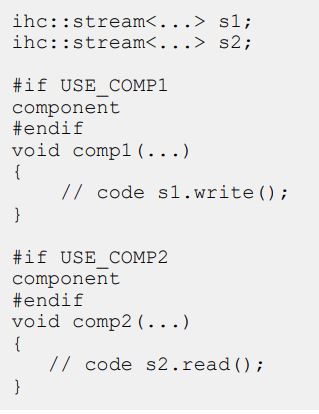

| La compilazione di alcuni progetti che contengono più componenti genera un errore relativo al riutilizzo del flusso. | Se riscontri questo problema, compila ciascun componente del progetto separatamente. Potrebbe essere necessario aggiungere macro al codice per consentire la compilazione separata di ciascun componente. | |

| Considera il seguente esampon: | ||

|

||

Archivi delle note di rilascio di Intel Synthesis Compiler Pro Edition

Per le versioni più recenti e precedenti di questa guida per l'utente, fare riferimento alle note sulla versione di Intel HLS Compiler Pro Edition. Se una versione del software non è elencata, si applicano le note sulla versione della versione software precedente.

Cronologia delle revisioni del documento per le note sulla versione di Intel HLS Compiler Pro Edition versione 22.4

| Versione del documento | Versione Intel Quartus Prime | Cambiamenti |

| 2022.12.19 | 22.4 | • Versione iniziale. |

Documenti / Risorse

|

Intel High Level Synthesis Compiler Edizione Pro [pdf] Istruzioni Versione 22.4, Versione 23.4, Compilatore di sintesi di alto livello Pro Edition, Compilatore di sintesi di alto livello, Pro Edition |