SmartFusion2MSS

SmartFusion2MSS

Creazione di un design utilizzando le interfacce MSS Fabric

Guida per l'utente

Introduzione

Il sottosistema microcontrollore SmartFusion2 (MSS) offre quattro diversi controller di interfaccia tessuto (FIC):

- DDR_FIC

- SMC_FIC

- FIC_0 e FIC_1, a seconda del dispositivo

Questi blocchi di interfaccia consentono all'MSS di interfacciarsi con la logica implementata nel fabric and vice dell'FPGA

versa.

Il DDR_FIC viene utilizzato quando si configura il blocco MSS DDR (MDDR) in modo tale che il DDR esterno

è possibile accedere alla memoria da un fabric master FPGA tramite un'interfaccia AXI o 2 interfacce AHBLite AMBA.

SMC_FIC viene utilizzato quando si configura il blocco MSS DDR in modalità Single Date Rate (SDR). In questa configurazione, l'MSS accede a DRAM Single Data Rate o memorie asincrone esterne tramite un controller di memoria software istanziato nella struttura FPGA, come CoreSDR_AXI. SMC_FIC è un'interfaccia AMBA slave AXI o AHBLite. Le interfacce DDR_FIC e SMC_FIC si escludono a vicenda; ne è attivo solo uno alla volta.

Le interfacce FIC consentono di estendere in modo naturale il bus MSS AMBA nella struttura FPGA. Sono disponibili fino a due istanze FIC per MSS a seconda del dispositivo selezionato. La prima istanza è denominata FIC_0 (che è disponibile su tutti i dispositivi) e la seconda è denominata FIC_1 (potrebbe non essere presente nei dispositivi più piccoli). È possibile configurare il FIC come interfaccia AMBA APB3 o AHBLite a seconda delle esigenze di progettazione. In ciascuna modalità è disponibile un'interfaccia bus master e una slave. In altre parole, un master nel fabric può interfacciarsi con uno slave nell'MSS e un master nell'MSS può interfacciarsi con uno slave nel fabric.

Ciascun sottosistema Fabric Interface può operare su una diversa frequenza di clock, definita come un rapporto del clock principale MSS M3_CLK.

L'architettura SmartFusion2 impone regole relative ai domini di clock tra Fabric Interfaces e Fabric FPGA. Questo documento fornisce una guida su come costruire correttamente tali sistemi.

Alto livello View

La Figura 1 e la Figura 2 mostrano come l'MSS si connette al fabric FPGA tramite i vari Fabric Interface Controller (FIC). La Figura 1 mostra uno schema a blocchi generale quando si utilizza DDR_FIC (memoria DDR esterna) e la Figura 2 mostra uno schema a blocchi per quando si utilizza SMC_FIC (memoria SDR esterna).

I diagrammi mostrano i sottoblocchi MSS essenziali per collegare l'MSS alla struttura FPGA. Il sottoblocco FIC può essere utilizzato o meno nella tua applicazione. Potresti anche non utilizzare le interfacce DDR_FIC o SMC_FIC nel tuo progetto. Tuttavia, ciò non modifica i requisiti generali su come creare un progetto con uno o più blocchi FIC utilizzati nel progetto.

Figura 1 • Diagramma a blocchi Fabric da MSS a FPGA – Modalità DDR_FIC

Figura 1 • Diagramma a blocchi Fabric da MSS a FPGA – Modalità DDR_FIC  Figura 2 • Diagramma a blocchi del fabric da MSS a FPGA – Modalità SMC_FIC

Figura 2 • Diagramma a blocchi del fabric da MSS a FPGA – Modalità SMC_FIC

Il MSS contiene:

- Matrice AHB_Bus; tutte le transazioni nell'MSS passano attraverso questo blocco.

- Controller DDR - si interfaccia con DDR_FIC.

- Sottoblocco DDR_FIC (SMC_FIC) (utilizzato se si abilita il percorso Fabric FPGA a DDR nel configuratore MSS_MDDR).

- Sottoblocco FIC_0.

- Sottoblocco FIC_1 (solo nei dispositivi più grandi).

- Sottoblocco FIC_2 (per l'inizializzazione APB di SERDES e DDR esterni).

- Sottoblocco MSS_CCC necessario per configurare gli orologi FIC relativi all'orologio principale MSS (M3_CLK).

- Sottoblocco MSS_RESET che genera i reset interni MSS e il segnale MSS_RESET_N_M2F che guida la struttura FPGA.

Il tessuto FPGA contiene:

- Tre sottosistemi FIC (DDR_FIC, FIC_0 e FIC_1).

- Fabric CCC – FAB_CCC – necessario per generare i clock che guidano il sottosistema FIC fabric FPGA e la porta MCCC_CLK_BASE sul blocco MSS.

- Segnale di clock di riferimento FAB_CCC: può essere uno degli oscillatori su chip, un oscillatore a cristallo esterno, un clock generato internamente al tessuto o dall'esterno del chip.

Il diagramma a blocchi mostra anche la rete dell'orologio in rosso e la rete di ripristino in blu scuro.

Questo documento discute ciascuno di questi blocchi e descrive come collegare gli orologi e i reset.

Configuratore MSS

Questo documento fa riferimento a determinati sottoblocchi MSS che devono essere configurati come parte della creazione di un progetto in cui l'MSS si interfaccia alla struttura FPGA tramite i sottoblocchi FIC. Questi blocchi sono evidenziati in rosso nella Figura 1-1.

Figura 1-1 • Configuratore MSS

Figura 1-1 • Configuratore MSS

Azioni del configuratore SmartDesign e MSS

Ci sono diverse azioni comuni a cui si fa riferimento in questo documento; sono riassunti nel seguente elenco:. Se hai familiarità con SmartDesign e MSS puoi saltare alla sezione successiva.

Istanziare un core – L'azione di selezionare un core dal catalogo IP del SoC Libero, trascinando e rilasciando quel core su uno SmartDesign Canvas.

Configurazione di un nucleo – L'azione di aprire il configuratore per un'istanza di quel core nel canvas, selezionare una particolare configurazione ed eseguirne il commit facendo clic su OK nella finestra di dialogo del configuratore. Come risultato di tale azione, solo le porte pertinenti alla configurazione corrente sono visibili e disponibili per l'uso.

Istanziare un componente – L'azione di selezionare un componente nella Gerarchia di progettazione del SoC Libero, trascinando e rilasciando quel componente su una tela di SmartDesign.

Creazione di un'istanza di un componente conforme AMBA personalizzato: l'azione di selezionare un componente HDL+ nella gerarchia di progettazione del SoC Libero, trascinando e rilasciando quel componente su uno SmartDesign Canvas.

L'utilizzo della funzione HDL+ consente di aggiungere interfacce bus (BIF) conformi AMBA al normale modulo HDL.

Configurazione di un componente – L'azione di aprire il configuratore per un componente istanziato su SmartDesign Canvas o dalla Gerarchia di progettazione, selezionare una particolare configurazione e confermarla facendo clic su OK nella finestra di dialogo del configuratore. Come risultato di tale azione, tutte le istanze su quel componente nel progetto Libero SoC sono interessate e devono essere aggiornate. Quando un'istanza viene aggiornata con il componente più recente, solo le porte pertinenti alla configurazione corrente sono visibili e disponibili per l'uso.

Abilitazione di un sottoblocco MSS – Alcuni sottoblocchi MSS possono essere abilitati o disabilitati, a indicare che sono utilizzati nell'applicazione corrente. Tutti i sottoblocchi non utilizzati devono essere disabilitati.

Configurazione di un sottoblocco MSS – L'azione di aprire il configuratore per quel sottoblocco nel configuratore MSS, selezionare una particolare configurazione e confermarla facendo clic su OK nella finestra di dialogo del configuratore, quindi salvare la configurazione MSS. Come risultato di queste azioni, il componente MSS ha una nuova configurazione e potenzialmente una nuova interfaccia di porta. Quando l'istanza di MSS viene aggiornata con l'ultimo componente, solo le porte MSS pertinenti alla configurazione corrente sono visibili e disponibili per l'uso.

Creazione di un sottosistema fabric FPGA – L'azione di istanziare, configurare core e componenti in uno SmartDesign Canvas e collegarli insieme e al componente MSS istanziato già in quel particolare SmartDesign.

Configurazione del sottosistema DDR_FIC

Per configurare/creare un sottosistema DDR_FIC, è necessario:

- Configura MSS MDDR per esporre l'interfaccia DDR_FIC

- Crea il sottosistema DDR_FIC fabric FPGA includendo istanziazione/configurazione/connettività per:

– Bus AXI o AHBLite

– Master/i bus AXI o AHBLite

– Altri master e periferiche sul bus come richiesto dall'applicazione

– Orologi e reset; fare riferimento a "Configurazione degli orologi del sottosistema FIC" a pagina 23 e "Configurazione del ripristino del sottosistema FIC" a pagina 27

Questi passaggi sono descritti in dettaglio di seguito.

Passaggio 1: configurare il sottoblocco MSS MDDR per esporre l'interfaccia del bus DDR_FIC

L'interfaccia DDR_FIC viene esposta quando l'applicazione deve accedere alla memoria DDR esterna dal fabric FPGA. In questa configurazione, il sottoblocco MDDR espone l'interfaccia DDR_FIC, che è un'interfaccia bus slave AXI o AHBLite (BIF) (Figura 3-1).

Figura 3-1 • Configurazione MSS DDR con accesso da FPGA Fabric

Figura 3-1 • Configurazione MSS DDR con accesso da FPGA Fabric

Passaggio 2: creare il sottosistema FPGA Fabric DDR_FIC

In base al tipo di connessione del bus FPGA selezionato (AXI, Single AHBLite o Two AHBLite), è necessario creare un sottosistema che corrisponda alla selezione.

Sottosistema DDR_FIC/AXI

- Crea un'istanza e configura il core IP CoreAXI dalla finestra Catalogo. Abilita gli slot che prevedi di utilizzare per la tua applicazione e la quantità di memoria per slot che corrisponde ai tuoi requisiti di progettazione. Poiché stai indirizzando una memoria DDR esterna, la selezione della dimensione dello slot dovrebbe corrispondere allo spazio che prevedi di indirizzare dal fabric master FPGA. (Figura 3-2).

Figura 3-2 • Configurazione CoreAXI

Figura 3-2 • Configurazione CoreAXI - Crea un'istanza e configura il core o il componente master conforme ad AMBA AXI destinato a masterizzare il bus AXI. Se la tua applicazione richiede più di un master sul bus CoreAXI, istanzia anche il secondo master.

- Collegare il sottosistema:

– Collegare la porta BIF (Mirrored-Master Bus Interface) M0 (M1) di CoreAXI alla porta BIF master delle istanze core master (Figura 3-3).

– Collegare la porta BIF slave MSS DDR_FIC – MDDR_DDR_AXI_SLAVE – allo slot slave con mirroring corretto del bus CoreAXI in base ai requisiti della mappa di memoria. Se hai altri slave su quel bus, collegali anche loro, secondo la tua mappa di memoria.

– Orologi e reset; fare riferimento a "Configurazione degli orologi del sottosistema FIC" a pagina 23 e "Configurazione del ripristino del sottosistema FIC" a pagina 27.

Figura 3-3 • Sottosistema DDR_FIC AXI

Figura 3-3 • Sottosistema DDR_FIC AXI

Sottosistema DDR_FIC/Single-AHBLite

- Crea un'istanza e configura il core IP CoreAHBLite dal catalogo. Abilitare gli slot che si prevede di utilizzare per l'applicazione come mostrato nella Figura 3-4. In questo esample, CoreAHBLite è configurato per indirizzare uno spazio di memoria RAM DDR da 4 GB utilizzando slot0 dal master M0. Poiché stai indirizzando una memoria DDR esterna, la selezione della dimensione dello slot dovrebbe corrispondere alla quantità di spazio di memoria DDR che prevedi di indirizzare dal fabric master FPGA.

Figura 3-4 • Core AHBLite – Configurazione master regione combinata

Figura 3-4 • Core AHBLite – Configurazione master regione combinata - Crea un'istanza e configura il core master o il componente conforme ad AMBA AHBLite che deve essere masterizzato sul bus CoreAHBLite. Se la tua applicazione richiede più di un master sul bus CoreAHBLite, istanzia anche i master aggiuntivi. Sul bus CoreAHBLite sono supportati fino a quattro master.

- Collegare il sottosistema:

– Collegare la porta BIF (Mirrored-Master Bus Interface) M0 (M1) di CoreAHBLite alla porta BIF master delle istanze core master.

– Collegare la porta MSS DDR_FIC slave BIF – MDDR_DDR_AHB0_SLAVE – all'apposito slot mirrored-slave del bus CoreAHBLite (S0 in questo example) secondo i requisiti della tua mappa di memoria. Se hai altri slave su quel bus, collegali così come per la tua mappa di memoria.

– Orologi e reset; fare riferimento a "Configurazione degli orologi del sottosistema FIC" a pagina 23 e "Configurazione del ripristino del sottosistema FIC" a pagina 27.

Figura 3-5 • Sottosistema DDR_FIC AHBLite

Figura 3-5 • Sottosistema DDR_FIC AHBLite

Sottosistema DDR_FIC/Due AHBLite

Quando si seleziona l'opzione delle due interfacce AHBLite per MDDR, un BIF aggiuntivo, MDDR_DDR_AHB1_SLAVE BIF, viene esposto al componente MSS per consentire la connessione al nuovo slave.

Per questa configurazione, ripetere i passaggi per una singola configurazione AHBLite per l'interfaccia BIF MDDR_DDR_AHB1_SLAVE esposta sul componente MSS.

Sebbene SMC_FIC possa essere utilizzato come interfaccia bus AXI o AHBLite, questo documento descrive solo come utilizzare l'interfaccia SMC_FIC configurata in modalità AXI per connettersi al core CoreSDR_AXI. Quel nucleo è un controller RAM SDR basato su AXI utilizzato per connettere, in questo caso, l'MSS a un componente di memoria SDR (Single Data Rate) esterno. Puoi facilmente dedurre come utilizzare l'interfaccia AHBLite dalla seguente descrizione; i passaggi sono molto simili. L'interfaccia AXI è un'interfaccia più efficiente ed è l'opzione preferita.

Per configurare/creare un sottosistema SMC_FIC è necessario:

- Configura MSS MDDR per esporre l'interfaccia SMC_FIC

- Creare il sottosistema DDR_FIC del fabric FPGA, inclusa la creazione di istanze/configurazione/connettività per:

– bus CoreAXI

– NucleoSDR_AXI

– Altri master e periferiche sul bus come richiesto dall'applicazione

– Orologi e reset; fare riferimento a "Configurazione degli orologi del sottosistema FIC" a pagina 23 e "Configurazione del ripristino del sottosistema FIC" a pagina 27

Questi passaggi sono descritti in dettaglio di seguito.

Passaggio 1: configurare il sottoblocco MSS MDDR per esporre l'interfaccia bus SMC_FIC

L'interfaccia SMC_FIC viene esposta quando l'applicazione deve accedere a una memoria SDR esterna tramite il fabric FPGA. In questa configurazione, il sottoblocco MDDR espone l'interfaccia SMC_FIC, che è un'interfaccia bus master AXI o AHBL (BIF) (Figura 4-1).

- Fare clic con il pulsante destro del mouse sul controller MDDR all'interno di MSS Configurator e scegliere Configura.

- Selezionare Usa un'interfaccia AXI.

- Fare clic su OK.

Figura 4-1 • Configurazione del controller di memoria software MDDR

Figura 4-1 • Configurazione del controller di memoria software MDDR

- Aggiorna il componente MSS con la modifica.

(Fai clic con il pulsante destro del mouse sul componente MSS e scegli Aggiorna istanze con il componente più recente). MDDR_SMC_AXI_MASTER è esposto come porta di interfaccia bus del componente MSS.

Passaggio 2: creare il sottosistema FPGA Fabric SMC_FIC

- Istanziare e configurare il CoreAXI in modo tale che lo slot master M0 sia abilitato per lo slot slave S0, come mostrato nella Figura 4-2. Poiché stai indirizzando una memoria esterna tramite un controller di memoria software, la selezione della dimensione dello slot dovrebbe corrispondere alla quantità di spazio di memoria esterna che prevedi di indirizzare dal processore Cortex-M3 o da qualsiasi scrittura master su quella memoria esterna tramite il bridge MSS DDR.

Figura 4-2 • Configurazione CoreAXI – Modalità SMC_FIC

Figura 4-2 • Configurazione CoreAXI – Modalità SMC_FIC - Dal catalogo IP, crea un'istanza e configura CoreSDR_AXI in modo che corrisponda ai parametri della memoria esterna.

- Collegare il sottosistema (Figura 4-3):

– Collegare la porta BIF del master MSS SMC_FIC – MDDR_SMC_AXI_MASTER – al master mirrored M0 del bus CoreAXI.

– Collegare la porta BIF (Mirrored-Slave Bus Interface) S0 di CoreAXI alla porta BIF slave dell'istanza core CoreSDR_AXI.

– Orologi e reset; fare riferimento a "Configurazione degli orologi del sottosistema FIC" a pagina 23 e "Configurazione del ripristino del sottosistema FIC" a pagina 27.

Figura 4-3 • Connessioni del sottosistema SMC_FIC

Figura 4-3 • Connessioni del sottosistema SMC_FIC

Configurazione dei sottosistemi FIC

Per configurare/creare un sottosistema FIC è necessario:

- Configurare MSS FIC per esporre l'interfaccia FIC

- Crea il sottosistema FIC fabric FPGA includendo istanziazione/configurazione/connettività per:

– Bus APB3 o AHBLite

– Configurazione master e/o periferiche conformi ad APB3 e AHBLite e connessione sul bus come richiesto dall'applicazione

– Orologi e reset; fare riferimento a "Configurazione degli orologi del sottosistema FIC" a pagina 23 e "Configurazione del ripristino del sottosistema FIC" a pagina 27

Questi passaggi sono descritti in dettaglio di seguito.

Passaggio 1: configurare il sottoblocco MSS FIC

- Richiama il configuratore FIC e fai clic con il pulsante destro del mouse su FIC_0 o FIC_1 per aprire il configuratore FIC.

- Nel configuratore per il gruppo di configurazione MSS to FPGA Fabric Interface selezionare:

– Il tipo di interfaccia AHBLite o APB3

– Se si intende utilizzare l'interfaccia come master della struttura FPGA

– Se si intende utilizzare l'interfaccia come slave masterizzato dalla struttura FPGA (Figura 5-1)

Figura 5-1 • Opzioni di interfaccia fabric da MSS a FPGA

Figura 5-1 • Opzioni di interfaccia fabric da MSS a FPGA - Se si utilizza un'interfaccia AHBLite, è anche possibile utilizzare le opzioni AHBLite avanzate per selezionare la modalità bypass o esporre la porta ID master se si è selezionata l'interfaccia per agire come master dell'infrastruttura (Figura 5-2).

Figura 5-2 • Opzioni AHBLite avanzate

Figura 5-2 • Opzioni AHBLite avanzate

Passaggio 2: creare il sottosistema FIC Fabric FPGA

Per ogni interfaccia FIC esposta, master e slave, è necessario creare un'istanza di un bus (CoreAHBLite o CoreAPB3) che corrisponda al tipo selezionato. A seconda del ruolo dell'interfaccia (master/slave) e del tipo (AHBLite/APB3), il bus deve essere configurato come segue:

Maestro/AHBLite

Crea un'istanza e configura il bus CoreAHBLite come segue:

- Seleziona l'opzione Spazio di memoria che corrisponde ai tuoi requisiti:

– Se sono necessari meno di 16 MB di spazio indirizzi di tutte le periferiche, selezionare l'opzione come mostrato nella Figura 5-3. Questa modalità fornisce 16 slot da 16 MB che possono essere utilizzati per collegare fino a 16 slave AHBLite.

Figura 5-3 • Configurazione dello spazio di memoria Master/AHBLite – 16 MB per slot

Figura 5-3 • Configurazione dello spazio di memoria Master/AHBLite – 16 MB per slot

– Se sono necessari più di 16 MB e meno di 256 MB di spazio indirizzi per qualsiasi periferica, selezionare l'opzione come mostrato nella Figura 5-4. Questa modalità fornisce 16 slot da 256 MB che possono essere utilizzati per collegare fino a 16 slave AHBLite.

Figura 5-4 • Configurazione dello spazio di memoria Master/AHBLite – 256 MB per slot

Figura 5-4 • Configurazione dello spazio di memoria Master/AHBLite – 256 MB per slot - Abilitare gli slot che si stanno utilizzando per l'applicazione (Figura 5-5). La migliore pratica consiste nell'utilizzare M1 per gli accessi allo slot come mostrato nella Figura 4-2 a pagina 15.

Nota: Utilizzare M1 se si prevede di creare un sottosistema multimaster in cui si dispone di un master nell'infrastruttura che richiede la funzione di rimappatura e quindi deve essere connesso a M0.

– Se è stata selezionata l'opzione 16 MB per slot, non ci sono restrizioni sugli slot che possono essere utilizzati.

– Se è stata selezionata l'opzione 256 MB per slot, è possibile utilizzare solo gli slot compatibili con la selezione delle regioni dell'indirizzo di memoria fabric dell'istanza FIC. Ciascuna regione dell'indirizzo di memoria FIC ha una dimensione di 256 MB. Le sei regioni di memoria FIC sono riassunte nella Tabella 5-1.

Tabella 5-1 • Regioni degli indirizzi e slot compatibili per l'opzione da 256 MB per slot

Regione dell'indirizzo di memoria Slot compatibili 30000000-3FFFFFFFF 3 50000000-5FFFFFFFF 5 70000000-7FFFFFFFF 7 80000000-8FFFFFFFF 8 90000000-9FFFFFFFF 9 F0000000-FFFFFFFF 15 (Donna)  Figura 5-5 • Configurazione accesso master Master/AHBLite

Figura 5-5 • Configurazione accesso master Master/AHBLite - Crea un'istanza e configura core periferici conformi ad AHBLite e/o componenti conformi ad AHBLite personalizzati.

- Collegare il sottosistema:

– Collegare la porta M1 dell'interfaccia bus master mirroring (BIF) di CoreAHBLite alla porta BIF master MSS – FIC_0/1_AHB_MASTER – come mostrato nella Figura 5-6.

– Collegare gli slave AHBLite agli slot appropriati in base ai requisiti della mappa di memoria.

– Orologi e reset; fare riferimento a "Configurazione degli orologi del sottosistema FIC" a pagina 23 e "Configurazione del ripristino del sottosistema FIC" a pagina 27.

Figura 5-6 • Sottosistema FIC Master/AHBLite

Figura 5-6 • Sottosistema FIC Master/AHBLite

Maestro/APB3

Crea un'istanza e configura il bus CoreAPB3 come segue:

- Selezionare le opzioni di configurazione dell'indirizzo come mostrato nella Figura 5-7. Questa modalità fornisce sedici slot da 16 MB che possono essere utilizzati per collegare fino a sedici slave compatibili con APB3. Se hai bisogno di slot con più memoria, puoi combinare più slave per creare uno slot più grande. Fare riferimento alla Guida per l'utente di CoreAPB3 per ulteriori dettagli su questa opzione.

Figura 5-7 • Configurazione indirizzo Master/APB3

Figura 5-7 • Configurazione indirizzo Master/APB3 - Abilitare gli slot che si stanno utilizzando per l'applicazione, come mostrato nella Figura 5-8.

Figura 5-8 • Configurazione degli slot master/APB3 slave

Figura 5-8 • Configurazione degli slot master/APB3 slave - Crea un'istanza e configura core periferici conformi ad APB3 e/o componenti conformi ad APB3 personalizzati.

- Collegare il sottosistema:

– Collegare la porta BIF (Mirrored-Master Bus Interface) CoreAPB3 alla porta BIF master MSS FIC_0/1_APB_MASTER, come mostrato nella Figura 5-9.

– Collegare gli slave APB3 agli slot appropriati secondo i requisiti della mappa di memoria.

– Orologi e reset; fare riferimento a "Configurazione degli orologi del sottosistema FIC" a pagina 23 e "Configurazione del ripristino del sottosistema FIC" a pagina 27.

Figura 5-9 • Sottosistema FIC Master/APB3

Figura 5-9 • Sottosistema FIC Master/APB3

Schiavo/AHBLite

Non disponibile al momento

Schiavo/APB3

Non disponibile al momento

Configurazione degli orologi del sottosistema FIC

Per creare la corretta configurazione dell'orologio e la connettività, è necessario:

- Configura gli orologi MSS CCC FIC

- Crea un'istanza e configura un core CCC fabric FPGA

- Collegare le reti di clock per ciascun sottosistema FIC

- Collegare la porta MSS CLK_BASE alla corretta rete di clock del sottosistema FIC fabric FPGA

L'architettura SmartFusion2 impone una serie di regole che devono essere seguite affinché tutti i sottosistemi FIC interagiscano correttamente tra la logica MSS e la logica fabric FPGA. Queste regole sono definite di seguito e mostrate nella Figura 6-1.

- Ogni sottosistema FIC fabric FPGA deve essere pilotato da un clock la cui frequenza di clock corrisponda alla frequenza definita, per quel particolare sottosistema, nel configuratore MSS CCC.

- Tutti i clock del sottosistema FIC fabric FPGA devono essere allineati con precisione; i clock possono avere frequenze diverse, ma i fronti di salita dei clock più lenti devono essere allineati ai fronti di salita dei clock più veloci.

- L'orologio del sottosistema FIC fabric FPGA con la frequenza più piccola deve pilotare MSS CLK_BASE.

- Se i fabric clock derivano da un fabric CCC (con PLL), l'uscita fabric CCC LOCK deve essere collegata alla porta MSS_CCC_CLK_BASE_PLL_LOCK. MSS CCC Fabric Alignment Clock Circuitry (FACC) monitora il segnale CLK_BASE PLL LOCK per garantire che CLK_BASE sia stabile prima di passare dall'orologio di standby (orologio utilizzato durante l'avvio del dispositivo) all'orologio configurato dall'utente derivato da CLK_BASE.

Figura 6-1 • Regole dell'orologio del sottosistema

Figura 6-1 • Regole dell'orologio del sottosistema

Seguire i passaggi seguenti per configurare le reti di clock per tutti i sottosistemi FIC.

Passaggio 1: configurare il sottoblocco MSS CCC

Per ogni blocco FIC (FIC_0, FIC_1 e DDR_FIC/SMC_FIC) utilizzato nel progetto, selezionare i divisori di clock in MSS Clock Configurator (MSS_CCC) come mostrato nella Figura 6-2. Figura 6-2 • Configurazione orologio MSS CCC FIC

Figura 6-2 • Configurazione orologio MSS CCC FIC

Nota che il campo CLK_BASE non è modificabile. La frequenza CLK_BASE, come imposto dall'architettura SmartFusion2, deve essere la frequenza minima di tutte le frequenze di clock FIC e viene calcolata automaticamente dal configuratore MSS CCC. Consultare “Fase 3: collegamento delle reti di clock dei sottosistemi FIC Fabric FPGA” a pagina 25 per ulteriori dettagli sulla configurazione di CLK_BASE.

Passaggio 2: configurare i clock FIC Fabric FPGA

Istanziare un fabric CCC (con PLL) e configurarlo per soddisfare le regole dell'orologio del sottosistema FIC descritte a pagina 23. In genere è necessario associare un'uscita globale (GLx) a ciascuno degli orologi FIC, specificare per ogni uscita la sua frequenza ( corrispondenti alle frequenze definite nell'MSS CCC) e hanno tutte le uscite globali derivate dall'uscita del PLL per garantire l'allineamento di fase (come mostrato in Figura 6-3).

Nota: Se due sottosistemi FIC hanno le stesse frequenze, non è necessario generare due uscite globali indipendenti dal fabric CCC; uno è sufficiente. Figura 6-3 • Tessuto CCC con PLL

Figura 6-3 • Tessuto CCC con PLL

Passaggio 3: collegare l'orologio dei sottosistemi FIC Fabric FPGA Reti

Connetti ciascun GLx di uscita globale CCC fabric al sottosistema FIC a cui è associato.

Passaggio 4: collegare la porta MSS CLK_BASE

Connetti il GLx di output globale CCC fabric più lento alla porta MSS CLK_BASE.

Passaggio 5: collegare la porta MSS MCCC_CLK_BASE_PLL_LOCK

Collegare l'uscita CCC LOCK del fabric alla porta MSS MCCC_CLK_BASE_PLL_LOCK.

Requisiti di analisi dei tempi

Esegui l'analisi della temporizzazione statica post-layout per assicurarti che il progetto soddisfi i requisiti di temporizzazione definiti nei configuratori CCC MSS CCC e FPGA fabric. Potrebbe essere necessario modificare M3_CLK o aumentare il rapporto di clock tra l'MSS e il tessuto per ottenere un progetto che superi l'analisi del tempo statico.

Configurazione del ripristino del sottosistema FIC

Per configurare il ripristino del sottosistema FIC:

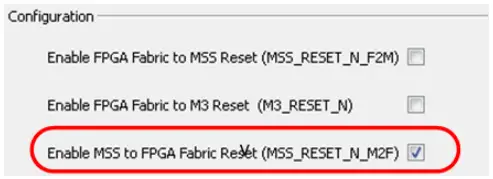

- Da MSS Configurator, configurare il sottoblocco MSS Reset per esporre la porta MSS_RESET_N_M2F.

Figura 7-1 • Configurare il sottoblocco di ripristino MSS

Figura 7-1 • Configurare il sottoblocco di ripristino MSS - Collegare la porta MSS_RESET_N_M2F a tutte le porte di ripristino dei sottosistemi FIC fabric FPGA.

Configurazione della mappa della memoria di sistema

Ogni periferica (AMBA AXI, AHBLite e APB3 slave) è identificata da un indirizzo dal punto master del sottosistema FIC di view. Di solito ci riferiamo alle relazioni complessive tra master e slave di un sottosistema come alla mappa della memoria di quel sottosistema. La mappa di memoria di un sottosistema può essere modificata in SmartDesign. Puoi anche view la mappa di memoria finale del tuo sistema quando generi l'intero sistema. La mappa di memoria fa parte del foglio dati generato per la "radice" del tuo progetto al momento della generazione.

Configurazione della mappa di memoria (comportamento generico di SmartDesign)

In SmartDesign, a una periferica viene assegnato un indirizzo su un bus in base all'indirizzo di base di quel bus nel sottosistema più il numero di slot su quel bus moltiplicato per la dimensione dello slot. Quindi la modifica del numero di slot per una periferica influisce di conseguenza sul suo indirizzo. La modifica dell'assegnazione dello slot per una periferica può essere eseguita collegando manualmente il BIF slave della periferica a un particolare BIF (slot) slave con mirroring del bus utilizzando gli strumenti di connettività SmartDesign disponibili nel Canvas. Questo può essere fatto anche modificando la mappa di memoria usando Modifica mappa di memoria, come mostrato nella Figura 8-1. Figura 8-1 • Modifica mappa memoria da SmartDesign Canvas

Figura 8-1 • Modifica mappa memoria da SmartDesign Canvas

Viene visualizzata la finestra di dialogo Modifica mappa memoria (Figura 8-2). Figura 8-2 • Finestra di dialogo Modifica mappa memoria

Figura 8-2 • Finestra di dialogo Modifica mappa memoria

Configurazione delle regioni di memoria per le interfacce FIC (MSS Master View)

Esistono sei regioni da 256 MB definite come regioni FIC da 0 a 5 nella mappa di memoria MSS. Ognuna di queste regioni può essere assegnata alle interfacce slave FIC_0 o FIC_1 in modo mutuamente esclusivo. È possibile selezionare a quale interfaccia slave FIC (0 o 1) assegnare tali regioni utilizzando il pulsante di opzione accanto a ciascuna regione nelle regioni dell'indirizzo del tessuto FPGA (MSS Master View) casella di gruppo (Figura 8-3).  Figura 8-3 • Regioni di indirizzo fabric FPGA (MSS Master View)

Figura 8-3 • Regioni di indirizzo fabric FPGA (MSS Master View)

Formula generale per il calcolo della mappa di memoria

I possibili indirizzi di base per le interfacce fabric FIC sono 0x30000000, 0x50000000, 0x70000000, 0x80000000, 0x90000000 e 0xF0000000. Consultare “Configurazione dei sottosistemi FIC” a pagina 17 per i dettagli su come configurare ciascuna istanza FIC per la mappatura a questi indirizzi.

Per AHBLite, la dimensione dello slot può essere 16 MB (0x01000000) o 256 MB (0x10000000).

Quando si utilizzano 16 MB per slot, è possibile utilizzare tutti gli slot da 0 a 16; l'indirizzo della periferica client può essere calcolato come indirizzo di base della regione di memoria FIC + (numero slot * 0x01000000). In questa configurazione, tutte le regioni sono in realtà alias l'una dell'altra poiché il core AHBLite non decodifica i bit di indirizzo [31:28]; gli slot vengono decodificati utilizzando i bit di indirizzo [27:24].

Quando si utilizzano 256 MB per slot, è possibile utilizzare solo gli slot 3, 5, 7, 8, 9 e F; l'indirizzo della periferica client può essere calcolato come indirizzo di base della regione di memoria FIC + (numero slot * 0x10000000). In questa configurazione, tutte le regioni indirizzano in modo univoco diversi slot mentre il core AHBLite decodifica gli slot utilizzando i bit di indirizzo [31:28]. In questa configurazione, per semplificare l'equazione della mappa di memoria, l'indirizzo di base è 0x00000000, invece di uno dei sei indirizzi fissi sopra definiti.

Example 1 (configurazione slot 16 MB):

Utilizzando la regione di memoria 0x50000000, se la periferica si trova nello slot numero 7, il suo indirizzo è: 0x50000000 + (0x7 * 0x01000000) = 0x57000000

Example 2 (configurazione slot 256 MB):

Utilizzando la regione di memoria 0x50000000, se la periferica si trova nello slot numero 15, il suo indirizzo è: 0x00000000 + (0xF * 0x10000000) = 0xF0000000

Viewing la mappa della memoria finale

Al momento, Libero SoC non genera una mappa di memoria corretta per i sistemi che utilizzano SmartFusion2 MSS.

Supporto prodotto

Microsemi SoC Products Group supporta i suoi prodotti con vari servizi di supporto, tra cui il servizio clienti, il centro di assistenza tecnica clienti, a websito, posta elettronica e uffici vendite in tutto il mondo. Questa appendice contiene informazioni su come contattare Microsemi SoC Products Group e utilizzare questi servizi di supporto.

Assistenza clienti

Contatta il servizio clienti per assistenza non tecnica sui prodotti, ad esempio prezzi dei prodotti, aggiornamenti dei prodotti, informazioni sull'aggiornamento, stato dell'ordine e autorizzazione.

Dal Nord America, chiamare 800.262.1060

Dal resto del mondo, chiama 650.318.4460

Fax, da qualsiasi parte del mondo, 408.643.6913

Centro assistenza tecnica clienti

Microsemi SoC Products Group dispone del suo Centro di assistenza tecnica clienti con ingegneri altamente qualificati che possono aiutarti a rispondere alle tue domande su hardware, software e progettazione relative ai prodotti Microsemi SoC. Il Customer Technical Support Center dedica molto tempo alla creazione di note applicative, risposte a domande comuni sul ciclo di progettazione, documentazione di problemi noti e varie domande frequenti. Quindi, prima di contattarci, visita le nostre risorse online. È molto probabile che abbiamo già risposto alle tue domande.

Supporto tecnico

Visita l'assistenza clienti webposto (www.microsemi.com/soc/support/search/default.aspx) per ulteriori informazioni e assistenza. Molte risposte disponibili sul ricercabile web risorsa includono diagrammi, illustrazioni e collegamenti ad altre risorse sul websito.

Websito

Puoi sfogliare una varietà di informazioni tecniche e non tecniche sulla home page del SoC, all'indirizzo www.microsemi.com/soc.

Contattare il centro di assistenza tecnica clienti

Ingegneri altamente qualificati gestiscono il Centro di assistenza tecnica. Il centro di assistenza tecnica può essere contattato tramite e-mail o tramite il gruppo di prodotti Microsemi SoC websito.

E-mail

Puoi comunicare le tue domande tecniche al nostro indirizzo e-mail e ricevere risposte via e-mail, fax o telefono. Inoltre, se hai problemi di progettazione, puoi inviare il tuo progetto tramite e-mail files per ricevere assistenza. Monitoriamo costantemente l'account e-mail per tutto il giorno. Quando ci invii la tua richiesta, assicurati di includere il tuo nome completo, il nome dell'azienda e le tue informazioni di contatto per un'elaborazione efficiente della tua richiesta.

L'indirizzo e-mail del supporto tecnico è soc_tech@microsemi.com.

I miei casi

I clienti di Microsemi SoC Products Group possono inviare e tenere traccia dei casi tecnici online accedendo a I miei casi.

Fuori dagli Stati Uniti

I clienti che necessitano di assistenza al di fuori dei fusi orari degli Stati Uniti possono contattare il supporto tecnico via e-mail (soc_tech@microsemi.com) o contattare un ufficio vendite locale. Gli elenchi degli uffici vendite sono disponibili all'indirizzo www.microsemi.com/soc/company/contact/default.aspx.

Supporto tecnico ITAR

Per il supporto tecnico sugli FPGA RH e RT regolati dalle normative sul traffico internazionale di armi (ITAR), contattaci tramite soc_tech_itar@microsemi.com. In alternativa, in I miei casi, seleziona Sì nell'elenco a discesa ITAR. Per un elenco completo degli FPGA Microsemi regolamentati da ITAR, visitare l'ITAR web pagina.

Microsemi Corporation (NASDAQ: MSCC) offre un portafoglio completo di semiconduttori soluzioni per: aerospaziale, difesa e sicurezza; impresa e comunicazioni; e mercati dell'energia industriale e alternativa. I prodotti includono dispositivi analogici e RF ad alte prestazioni e alta affidabilità, circuiti integrati a segnali misti e RF, SoC personalizzabili, FPGA e sottosistemi completi. Microsemi ha sede ad Aliso Viejo, in California. Scopri di più su www.microsemi.com.

© 2014 Microsemi Corporation. Tutti i diritti riservati. Microsemi e il logo Microsemi sono marchi di Microsemi Corporation. Tutti gli altri marchi e marchi di servizio sono di proprietà dei rispettivi proprietari.

5-02-00370-1/08.14

Sede aziendale Microsemi

Sede aziendale Microsemi

One Enterprise, Aliso Viejo CA 92656 USA

Negli USA: +1 Numero di telefono: 949-380-6100

Vendite: +1 Numero di telefono: 949-380-6136

Fax: +1 Numero di telefono: 949-215-4996

Documenti / Risorse

|

Microsemi SmartFusion2 MSS Creazione di un progetto [pdf] Guida utente SmartFusion2 MSS Creazione di un progetto |