CC1312PSIP

CC1312PSIP

SWRS293 – MAGGIO 2023

CC1312PSIP Sistema wireless in package SimpleLink™ sub-1 GHz

Caratteristiche

Microcontrollore wireless

- Potente processore Arm® Cortex® TI Co nfid -M48F da 4 MHz

- Memoria di programma flash da 352 KB

- 256KB di ROM per protocolli e funzioni di libreria

- 8 KB di cache SRAM

- 80KB di SRAM a bassissima dispersione con parità per un funzionamento ad alta affidabilità

- Driver di gestione multiprotocollo dinamico (DMM).

- La radio programmabile include il supporto per 2(G)FSK, 4-(G)FSK, MSK, OOK, IEEE 802.15.4 PHY e MAC

- Supporta l'aggiornamento via etere (OTA) Controller del sensore a bassissima potenza

- MCU autonomo con 4KB di SRAM

- Sample, archivia ed elabora i dati dei sensori

- Riattivazione rapida per il funzionamento a bassa potenza

- Periferiche definite dal software; tocco capacitivo, flussometro,

LCD Basso consumo energetico - Consumo MCU: – 2.9 mA in modalità attiva, CoreMark®

– 60 μA/MHz con CoreMark®

– Modalità standby 0.9 μA, RTC, 80KB di RAM

– Modalità di spegnimento da 0.1 μA, riattivazione su pin - Consumo del controller del sensore a bassissimo consumo:

– 30 μA in modalità 2 MHz

– 808 μA in modalità 24 MHz - Consumo radio:

– RX da 5.8 mA a 868 MHz

– TX da 28.7 mA a +14 dBm a 868 MHz

Supporto del protocollo wireless - Wi-SUN®

- mioty®

- M-Bus wireless

- SimpleLink™ TI 15.4-stack

- 6LowPAN

- Sistemi proprietari Radio ad alte prestazioni

- –119 dBm per la modalità a lungo raggio a 2.5 kbps

- –108 dBm a 50 kbps, 802.15.4, 868 MHz

Conformità normativa - Pre-certificato per:

– FCC CFR47 Parte 15 - Adatto per sistemi mirati alla conformità con:

– Ricevitore ETSI EN 300 220 cat. 1.5 e 2, EN 303 131, EN 303 204

– ARIB STD-T108

periferiche MCU - Le periferiche digitali possono essere instradate a 30 GPIO

- Quattro timer per uso generale a 32 bit o otto a 16 bit

- ADC a 12 bit, 200 kSampmeno/i, 8 canali

- DAC a 8 bit

- Due comparatori

- Sorgente di corrente programmabile

- Due UART, due SSI, I

- Orologio in tempo reale (RTC)

- Monitoraggio integrato della temperatura e della batteria

Abilitatori della sicurezza - Acceleratore crittografico AES a 128 e 256 bit

- Acceleratore hardware a chiave pubblica ECC e RSA

- SHA2 Accelerator (suite completa fino a SHA-512)

- Vero generatore di numeri casuali (TRNG)

Strumenti e software di sviluppo - Kit di sviluppo LP-CC1312PSIP

- Software SimpleLink™ CC13xx e CC26xx

Kit di sviluppo (SDK) - SmartRF™ Studio per una semplice configurazione radio

- Sensor Controller Studio per la creazione di applicazioni di rilevamento a bassa potenza

- Strumento di configurazione del sistema SysConfig

Campo di funzionamento - Alimentazione singola da 1.8 V a 3.8 V voltage

- Da –40 a +105°C (+14 dBm PA)

Tutti i componenti necessari integrati - Cristallo da 48 MHz: precisione RF ±10 ppm

- Cristallo da 32 kHz: precisione RTC ±50 ppm

- Componenti convertitori DC/DC e condensatori di disaccoppiamento

- Componenti front-end RF con uscita da 50 Ohm

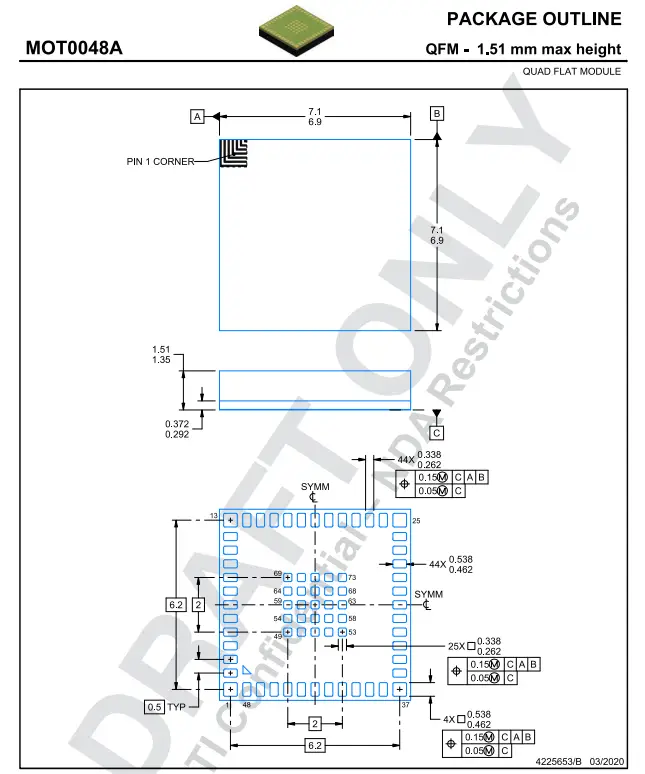

Pacchetto - MOT 7 mm × 7 mm (30 GPIO)

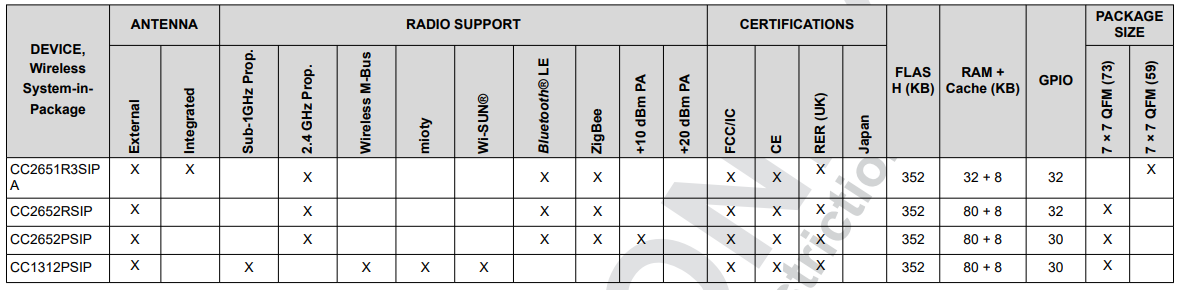

- Compatibile pin-to-pin con CC2652RSIP e CC2652PSIP

- Pacchetto conforme alla direttiva RoHS

![]() IMPORTANTE L'AVVISO alla fine di questa scheda tecnica riguarda disponibilità, garanzia, modifiche, utilizzo in applicazioni critiche per la sicurezza, questioni di proprietà intellettuale e altre importanti esclusioni di responsabilità. INFORMAZIONI ANTICIPATE per i prodotti di pre-produzione; Soggetto a modifiche senza preavviso.

IMPORTANTE L'AVVISO alla fine di questa scheda tecnica riguarda disponibilità, garanzia, modifiche, utilizzo in applicazioni critiche per la sicurezza, questioni di proprietà intellettuale e altre importanti esclusioni di responsabilità. INFORMAZIONI ANTICIPATE per i prodotti di pre-produzione; Soggetto a modifiche senza preavviso.

Applicazioni

- Sistemi ISM e SRD da 868 e 902 a 928 MHz 1 con larghezza di banda di ricezione fino a 4 kHz

- Automazione degli edifici

– Sistemi di sicurezza dell’edificio – rilevatore di movimento, serratura elettronica intelligente, sensore per porte e finestre, sistema di porte per garage, gateway

– HVAC – termostato, sensore ambientale wireless, controller del sistema HVAC, gateway

– Sistema di sicurezza antincendio – rilevatore di fumo e calore, centrale di allarme antincendio (FACP)

– Videosorveglianza – Telecamera di rete IP

– Ascensori e scale mobili – pannello di controllo principale dell'ascensore per ascensori e scale mobili - Infrastruttura di rete

– Contatori intelligenti: contatore dell’acqua, contatore del gas, contatore elettrico e contabilizzatori di costi di riscaldamento

– Comunicazioni di rete – comunicazioni wireless – applicazioni di sensori a lungo raggio

– Infrastruttura di ricarica per veicoli elettrici – Stazione di ricarica AC (pila).

– Altre energie alternative – raccolta di energia - Trasporti industriali – tracciabilità delle risorse

- Automazione e controllo di fabbrica

- Medico

- Apparecchiature di comunicazione

– Rete cablata: punti di accesso LAN wireless o Wi-Fi, router edge

Descrizione

Il dispositivo SimpleLink ™ CC1312PSIP è un modulo wireless System-in-Package (SiP) sub-1 GHz che supporta IEEE 802.15.4, oggetti intelligenti abilitati IPv6 (6LoWPAN), mioty, sistemi proprietari, incluso TI 15.4-Stack. Il microcontroller (MCU) CC1312PSIP è basato su un processore principale Arm M4F ed è ottimizzato per la comunicazione wireless a bassa potenza e il rilevamento avanzato nelle infrastrutture di rete, nell'automazione degli edifici, nell'automazione della vendita al dettaglio e nelle applicazioni mediche. Il CC1312PSIP ha una corrente di sospensione bassa di 0.9 μA con RTC e ritenzione di 80 KB di RAM. Oltre al processore principale Cortex® M4F, il dispositivo dispone anche di una CPU autonoma del controller del sensore a bassissimo consumo con capacità di riattivazione rapida. Come example, il controller del sensore è in grado di supportare ADC da 1 Hzampcorrente di sistema media di 1 μA.

Il CC1312PSIP ha un FIT (Failure-in-time) basso SER (Soft Error Rate) per una lunga durata operativa. La parità SRAM sempre attiva riduce al minimo il rischio di danneggiamento dovuto a potenziali eventi di radiazioni. Coerentemente con i requisiti del ciclo di vita di 10-15 anni o più di molti clienti, TI ha una politica sul ciclo di vita del prodotto con un impegno alla longevità del prodotto e alla continuità della fornitura, compreso il doppio approvvigionamento dei componenti chiave nel SIP. Il dispositivo CC1312PSIP fa parte della piattaforma MCU SimpleLink™, che comprende Wi-Fi®, Bluetooth® Low Energy, Thread, Zigbee, Wi-SUN®, Amazon Sidewalk, mioty, MCU sub-1 GHz e MCU host. CC1312PSIP fa parte di un portafoglio che include SIP da 2.4 GHz compatibili con i pin per un facile adattamento di un prodotto wireless a più standard di comunicazione. Il comune Software Development Kit (SDK) SimpleLink™CC13xx e CC26xx e lo strumento di configurazione del sistema SysConfig supportano la migrazione tra i dispositivi del portafoglio. Un numero completo di stack software, applicazioni esampi e le sessioni di formazione SimpleLink Academy sono inclusi nell'SDK. Per ulteriori informazioni, visitare Connettività wireless.

| NUMERO PARTE | PACCHETTO | DIMENSIONE CORPO (NOM) |

| CC1312PSIPMOT | QFM | 7.00 millimetri × 7.00 millimetri |

(1) Per le informazioni più aggiornate su componenti, pacchetti e ordini per tutti i dispositivi disponibili, consultare l'Addendum sull'opzione pacchetto in Informazioni su meccanica, imballaggio e ordinabilità oppure consultare il TI websito.

1 Consultare RF Core per ulteriori dettagli sugli standard di protocollo supportati, sui formati di modulazione e sulle velocità dei dati.

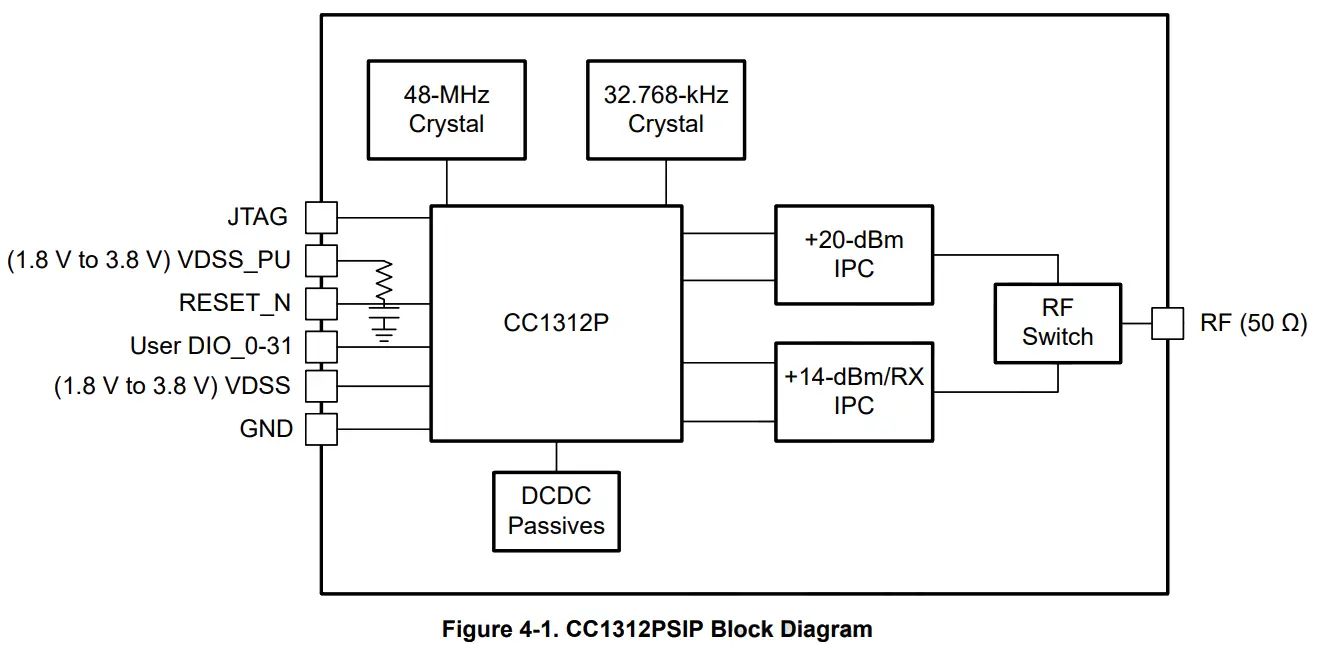

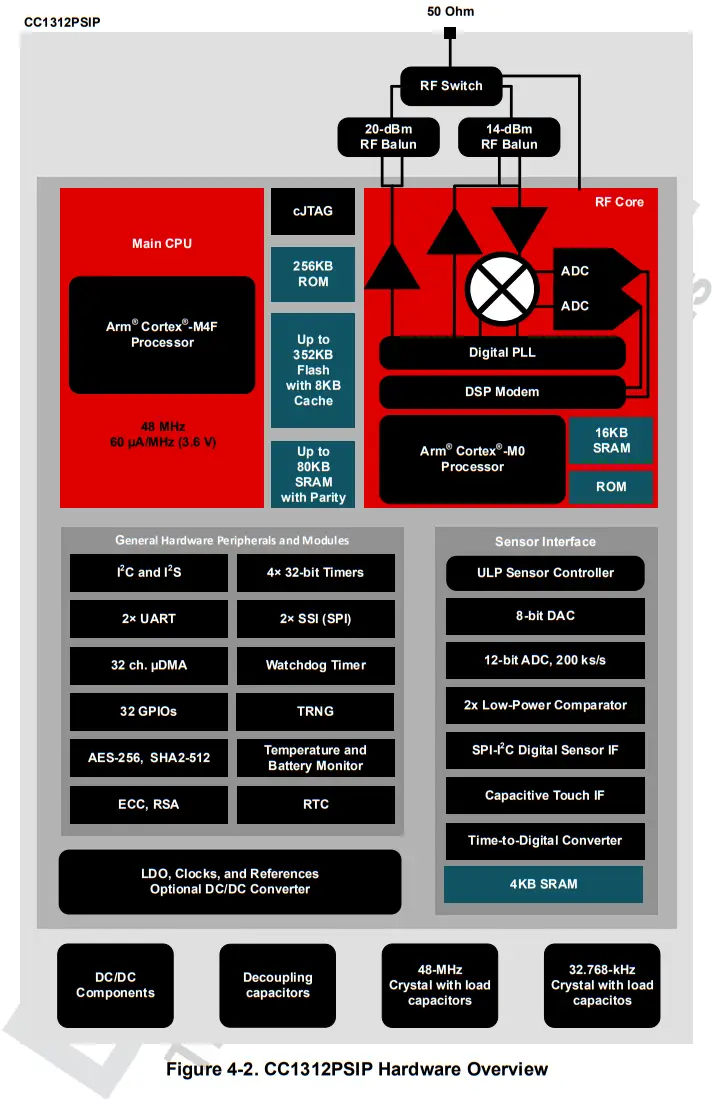

Diagramma a blocchi funzionale

Cronologia delle revisioni

NOTA: I numeri di pagina delle revisioni precedenti potrebbero differire dai numeri di pagina della versione corrente.

| DATA | REVISIONE | NOTE |

| Maggio-23 | * | Versione iniziale |

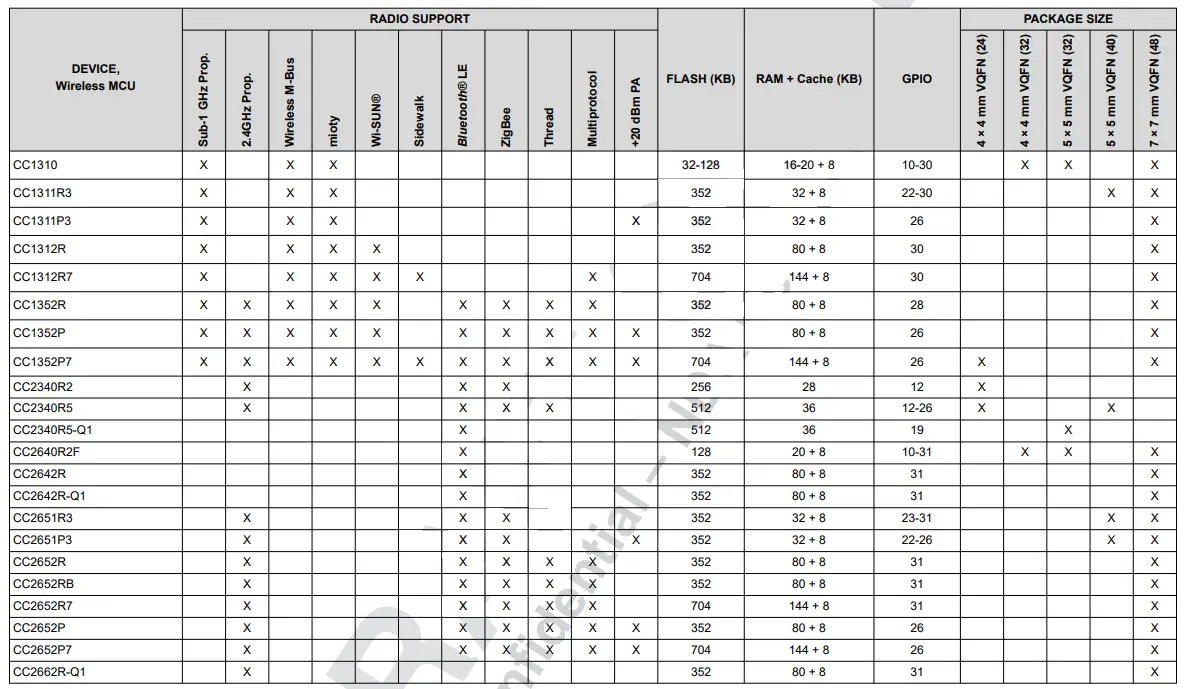

Confronto dei dispositivi

Configurazione e funzioni dei pin

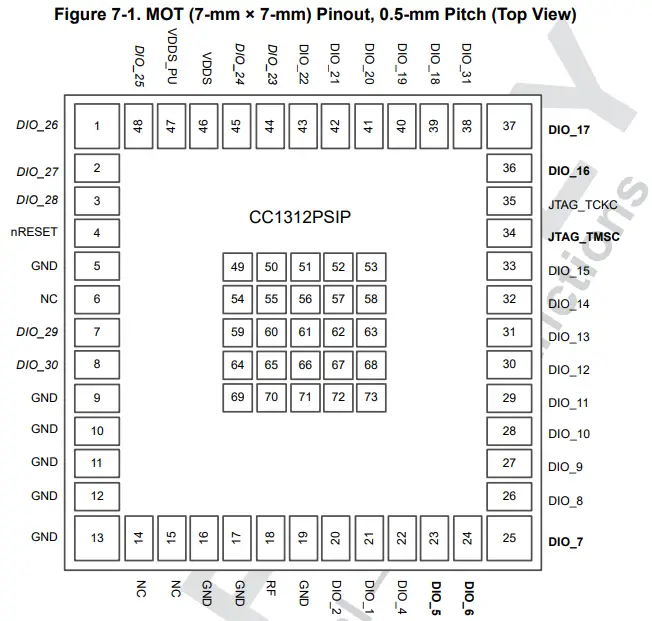

7.1 Schema dei pin – Pacchetto MOT (in alto View)

Figura 7-1. Pinout MOT (7 mm × 7 mm), passo 0.5 mm (superiore View)

I seguenti pin I/O contrassegnati in grassetto nella Figura 7-1 hanno capacità di pilotaggio elevate:

- Perno 23, DIO_5

- Perno 24, DIO_6

- Perno 25, DIO_7

- Perno 34, JTAG_TMSC

- Perno 36, DIO_16

- Perno 37, DIO_17

I seguenti pin I/O contrassegnati in corsivo nella Figura 7-1 hanno funzionalità analogiche:

- Perno 1, DIO_26

- Perno 2, DIO_27

- Perno 3, DIO_28

- Perno 7, DIO_29

- Perno 8, DIO_30

- Perno 44, DIO_23

- Perno 45, DIO_24

- Perno 48, DIO_25

7.2 Descrizioni dei segnali – Pacchetto MOT

Tabella 7-1. Descrizioni dei segnali – Pacchetto SIP

| SPILLO | Entrata/uscita | TIPO |

DESCRIZIONE |

|

| NOME |

NO. |

|||

| NC | 14 | Entrata/uscita | Digitale | Non connesso |

| DIO_1 | 21 | Entrata/uscita | Digitale | GPIO |

| DIO_10 | 28 | Entrata/uscita | Digitale | GPIO |

| DIO_11 | 29 | Entrata/uscita | Digitale | GPIO |

| DIO_12 | 30 | Entrata/uscita | Digitale | GPIO |

| DIO_13 | 31 | Entrata/uscita | Digitale | GPIO |

| DIO_14 | 32 | Entrata/uscita | Digitale | GPIO |

| DIO_15 | 33 | Entrata/uscita | Digitale | GPIO |

| DIO_16 | 36 | Entrata/uscita | Digitale | GPIO, JTAG_TDO, capacità di guida elevata |

| DIO_17 | 37 | Entrata/uscita | Digitale | GPIO, JTAG_TDI, capacità di guida elevata |

| DIO_18 | 39 | Entrata/uscita | Digitale | GPIO |

| DIO_19 | 40 | Entrata/uscita | Digitale | GPIO |

| DIO_2 | 20 | Entrata/uscita | Digitale | GPIO |

| DIO_20 | 41 | Entrata/uscita | Digitale | GPIO |

| DIO_21 | 42 | Entrata/uscita | Digitale | GPIO |

| DIO_22 | 43 | Entrata/uscita | Digitale | GPIO |

| DIO_23 | 44 | Entrata/uscita | Digitale o analogico | GPIO, capacità analogica |

| DIO_24 | 45 | Entrata/uscita | Digitale o analogico | GPIO, capacità analogica |

| DIO_25 | 48 | Entrata/uscita | Digitale o analogico | GPIO, capacità analogica |

| DIO_26 | 1 | Entrata/uscita | Digitale o analogico | GPIO, capacità analogica |

| DIO_27 | 2 | Entrata/uscita | Digitale o analogico | GPIO, capacità analogica |

| DIO_28 | 3 | Entrata/uscita | Digitale o analogico | GPIO, capacità analogica |

| DIO_29 | 7 | Entrata/uscita | Digitale o analogico | GPIO, capacità analogica |

| NC | 15 | Entrata/uscita | Digitale | Non connesso |

| DIO_30 | 8 | Entrata/uscita | Digitale o analogico | GPIO, capacità analogica |

| PIO_31 | 38 | Entrata/uscita | Digitale | Supporta solo funzionalità periferiche. Non supporta la funzionalità I/O per scopi generici. |

| DIO_4 | 22 | Entrata/uscita | Digitale | GPIO |

| DIO_5 | 23 | Entrata/uscita | Digitale | GPIO, capacità di guida elevata |

| DIO_6 | 24 | Entrata/uscita | Digitale | GPIO, capacità di guida elevata |

| DIO_7 | 25 | Entrata/uscita | Digitale | GPIO, capacità di guida elevata |

| DIO_8 | 26 | Entrata/uscita | Digitale | GPIO |

| DIO_9 | 27 | Entrata/uscita | Digitale | GPIO |

| Terra | 5 | — | — | Terra |

| Terra | 9 | — | — | Terra |

| Terra | 10 | — | — | Terra |

| Terra | 11 | — | — | Terra |

| Terra | 12 | — | — | Terra |

| Terra | 13 | — | — | Terra |

| Terra | 16 | — | — | Terra |

| Terra | 17 | — | — | Terra |

| Terra | 19 | — | — | Terra |

| Terra | 49-73 | — | — | Terra |

7.3 Connessioni per pin e moduli non utilizzati

Tabella 7-2. Connessioni per pin non utilizzati

| SPILLO | Entrata/uscita | TIPO |

DESCRIZIONE |

|

|

NOME |

NO. |

|||

| NC | 6 | — | — | Non connesso |

| nREIMPOSTA | 4 | I | Digitale | Reset, attivo basso. Resistore pullup interno e 100 nF interno a VDDS_PU |

| RF | 18 | — | RF | Porta RF da 50 ohm |

| JTAG_TCKC | 35 | I | Digitale | JTAG_TCKC |

| JTAG_TMSC | 34 | Entrata/uscita | Digitale | JTAG_TMSC, capacità di guida elevata |

| VDD | 46 | — | Energia | Alimentazione SIP principale da 1.8 V a 3.8 V |

| VDDS_PU | 47 | — | Energia | Alimentazione per ripristinare la resistenza pullup interna |

Specifiche

8.1 Valutazioni massime assolute

oltre l'intervallo di temperature operative in aria libera (se non diversamente specificato)(1) (2)

|

|

MINIMO | Massimo |

UNITÀ |

||

| VDD(3) | Volume di fornituratage | –0.3 | 4.1 | V | |

| Voltage su qualsiasi pin digitale(4) | –0.3 | VDD + 0.3, massimo 4.1 | V | ||

| Vino | Voltage sull'ingresso ADC | Voltage ridimensionamento abilitato | –0.3 | VDD |

V |

| Voltage scaling disabilitato, riferimento interno | –0.3 | 1.49 | |||

| Voltage ridimensionamento disabilitato, VDDS come riferimento | –0.3 | VDD / 2.9 | |||

| 10 | dBm | ||||

| TSTG | Temperatura di conservazione | –40 | 150 | °C | |

- Il funzionamento al di fuori dei limiti massimi assoluti può causare danni permanenti al dispositivo. I valori massimi assoluti non implicano il funzionamento funzionale del dispositivo a queste o altre condizioni oltre a quelle elencate nelle Condizioni operative consigliate. Se utilizzato al di fuori delle condizioni operative consigliate ma entro i limiti massimi assoluti, il dispositivo potrebbe non essere completamente funzionante e ciò potrebbe influire sull'affidabilità, sulla funzionalità, sulle prestazioni del dispositivo e ridurne la durata.

- Tutti i volumitagI valori sono rispetto al suolo, se non diversamente specificato.

- VDDS_DCDC, VDDS2 e VDDS3 devono avere lo stesso potenziale di VDDS.

- Compresi DIO con funzionalità analogica.

8.2 Valutazioni ESD

| VALORE | UNITÀ | ||||

| VED | Scarica elettrostatica | Modello del corpo umano (HBM), conforme a ANSI/ESDA/JEDEC JS-001(1) | Tutti i pin | ±1000 | V |

| Modello del dispositivo caricato (CDM), conforme a ANSI/ESDA/JEDEC JS-002(2) | Tutti i pin | ±500 | V | ||

- Il documento JEDEC JEP155 afferma che la HBM da 500 V consente una produzione sicura con un processo di controllo ESD standard.

- Il documento JEDEC JEP157 afferma che il CDM da 250 V consente una produzione sicura con un processo di controllo ESD standard.

8.3 Condizioni operative consigliate

oltre l'intervallo di temperature operative in aria libera (se non diversamente specificato)

|

|

MINIMO | Massimo |

UNITÀ |

|

| Temperatura ambiente operativa(1) (2) | –40 | 105 | °C | |

| Volume di alimentazione operativotage(VDDS) | 1.8 | 3.8 | V | |

| Volume di alimentazione operativotage (VDDS), modalità boost | VDDR = potenza di uscita RF inferiore a 1.95 GHz da 14 V +1 dBm amppiù vivace | 2.1 | 3.8 | V |

| Offerta in aumento voltage velocità di risposta | 0 | 100 | mV/μs | |

| Offerta in calo voltage velocità di risposta | 0 | 20 | mV/μs | |

(1) Il funzionamento alla temperatura operativa massima o in prossimità di essa per periodi prolungati comporterà una riduzione della durata.

(2) Per le caratteristiche di resistenza termica fare riferimento a .

8.4 Alimentatore e moduli

oltre l'intervallo di temperature operative in aria libera (se non diversamente specificato)

|

PARAMETRO |

MINIMO | TIPO | Massimo |

UNITÀ |

|

| Soglia VDDS Power-on-Reset (POR). | 1.1 – 1.55 | V | |||

| Rilevatore di cali di tensione VDDS (BOD) (1) | Soglia in aumento | 1.77 | V | ||

| Rilevatore di brown-out VDDS (BOD), prima dell'avvio iniziale (2) | Soglia in aumento | 1.70 | V | ||

| Rilevatore di cali di tensione VDDS (BOD) (1) | Soglia di caduta | 1.75 | V | ||

(1) Per la modalità boost (VDDR = 1.95 V), l'inizializzazione del software dei driver TI ridurrà i limiti BOD VDDS al massimo (circa 2.0 V)

(2) Il rilevatore di brown-out viene regolato all'avvio iniziale, il valore viene mantenuto finché il dispositivo non viene ripristinato tramite un ripristino POR o il pin RESET_N

8.5 Consumo energetico – Modalità di alimentazione

Quando misurato sul progetto di riferimento CC1312PSIP-EM con Tc = 25 °C, VDDS = 3.6 V con CC/CC abilitato, salvo diversa indicazione.

|

PARAMETRO |

CONDIZIONI DI PROVA | TIPO | UNITÀ | |

|

Consumo di corrente principale |

||||

| Icore | Reset | Ripristina. RESET_N pin affermato o VDDS inferiore alla soglia di ripristino all'accensione (4) | 36 | µA |

| Fermare | Spegnimento. Nessun orologio in esecuzione, nessuna conservazione | 150 | nA | |

| Standby con conservazione della cache | RTC funzionante, CPU, 80KB RAM e ritenzione (parziale) dei registri. RCOSC_LF | 0.9 | µA | |

| RTC in esecuzione, CPU, 80KB di RAM e ritenzione del registro (parziale) XOSC_LF | 1.0 | |||

| Standby con conservazione della cache | RTC in esecuzione, CPU, 80KB di RAM e ritenzione del registro (parziale) XOSC_LF | 2.8 | µA | |

| RTC in esecuzione, CPU, 80KB di RAM e ritenzione del registro (parziale) XOSC_LF | 2.9 | |||

| Oziare | Sistemi di alimentazione e RCOSC_HF alimentati da RAM | 590 | µA | |

| Icore | Attivo | MCU con CoreMark a 48 MHz RCOSC_HF | 2.89 | mA |

| Consumo di corrente periferico | ||||

| Iperi | Dominio di potere periferico | Corrente delta con dominio abilitato | 82 | µA |

| Dominio di alimentazione seriale | Corrente delta con dominio abilitato | 5.5 | ||

| Nucleo RF | Corrente delta con dominio di alimentazione abilitato, orologio abilitato, core RF inattivo | 179 | ||

| µDMA | Corrente delta con orologio abilitato, il modulo è inattivo | 54 | ||

| Timer | Corrente delta con orologio abilitato, il modulo è inattivo(3) | 68 | ||

| I2C | Corrente delta con orologio abilitato, il modulo è inattivo | 8.2 | ||

| I2S | Corrente delta con orologio abilitato, il modulo è inattivo | 22 | ||

| SSI | Corrente delta con orologio abilitato, il modulo è inattivo(2) | 70 | ||

| UART | Corrente delta con orologio abilitato, il modulo è inattivo(1) | 141 | ||

| CRITTOGRAFIA (AES) | Corrente delta con orologio abilitato, il modulo è inattivo | 21 | ||

| PCA | Corrente delta con orologio abilitato, il modulo è inattivo | 71 | ||

| TRNG | Corrente delta con orologio abilitato, il modulo è inattivo | 30 | ||

| Consumo del motore del controller del sensore | ||||

| ISCIE | Modalità attiva | 24 MHz, ciclo infinito | 808 | µA |

| Modalità a basso consumo | 2 MHz, ciclo infinito | 30.1 | ||

- Solo un UART in esecuzione

- È attivo un solo SSI

- Solo un GPTimer in esecuzione

- CC1312PSIP integra una resistenza pull-up da 100 kΩ su nRESET

8.6 Consumo energetico – Modalità radio

Quando misurato sul progetto di riferimento CC1312PSIP-EM con Tc = 25 °C, VDDS = 3.6 V con CC/CC abilitato, salvo diversa indicazione.

Using boost mode (increasing VDDR up to 1.95 V), will increase system current by 15% (does not apply to TX +14 dBm setting where this current is already included).

Le correnti Icore e Iperi rilevanti sono incluse nei numeri sottostanti.

|

PARAMETRO |

CONDIZIONI DI PROVA | TIPO |

UNITÀ |

|

| Corrente di ricezione radio, 868 MHz | 5.8 | mA | ||

| La radio trasmette la corrente PA normale | Impostazione potenza di uscita 0 dBm 868 MHz | 9.4 | mA | |

| Impostazione potenza in uscita +10 dBm 868 MHz | 17.3 | mA | ||

| La radio trasmette la modalità Boost corrente, PA normale | Impostazione potenza in uscita +14 dBm 868 MHz | 28.7 | mA | |

8.7 Caratteristiche della memoria non volatile (Flash).

Oltre l'intervallo di temperature operative in aria libera e VDDS = 3.0 V (se non diversamente specificato)

| PARAMETRO | CONDIZIONI DI PROVA | MINIMO | TIPO | Massimo |

UNITÀ |

| Dimensione del settore flash | 8 | KB | |||

| Cicli di cancellazione flash supportati prima del guasto, banco singolo(1) (5) | 30 | k Cicli | |||

| Cicli di cancellazione flash supportati prima del guasto, settore singolo(2) | 60 | k Cicli | |||

| Numero massimo di operazioni di scrittura per riga prima della cancellazione del settore(3) | 83 | Operazioni di scrittura | |||

| Conservazione del flash | 105 °C | 11.4 | Anni a 105°C | ||

| Il settore flash cancella la corrente | Corrente delta media | 10.7 | mA | ||

| Tempo di cancellazione del settore flash(4) | Cicli zero | 10 | ms | ||

| Cicli 30k | 4000 | ms | |||

| Corrente di scrittura Flash | Corrente delta media, 4 byte alla volta | 6.2 | mA | ||

| Tempo di scrittura Flash(4) | 4 byte alla volta | 21.6 | ms | ||

- Una cancellazione completa della banca viene conteggiata come un singolo ciclo di cancellazione su ciascun settore.

- È possibile cancellare individualmente fino a 4 settori designati dal cliente altre 30 volte oltre il limite di base della banca di 30 cicli

- Ogni wordline è larga 2048 bit (o 256 byte). Questa limitazione corrisponde a scritture di memoria sequenziali di almeno 4 (3.1) byte per scrittura su un'intera wordline. Se sono necessarie ulteriori scritture sulla stessa riga di parola, è necessaria la cancellazione di un settore una volta raggiunto il numero massimo di operazioni di scrittura per riga.

- Questo numero dipende dall'invecchiamento della Flash e aumenta nel tempo e nei cicli di cancellazione

- Interrompere il flash durante la modalità di cancellazione o di programmazione non è un'operazione sicura.

8.8 Caratteristiche di resistenza termica

| METRICA TERMICA | PACCHETTO | UNITÀ | |

| MOT (SIP) | |||

| PIN 73 | |||

| RθJA | Resistenza termica dalla giunzione all'ambiente | 48.7 | °C/W(1) |

| RθJC(in alto) | Resistenza termica dalla giunzione alla custodia (superiore). | 12.4 | °C/W(1) |

| RθJB | Resistenza termica dalla giunzione alla scheda | 32.2 | °C/W(1) |

| ψJT | Parametro di caratterizzazione dalla giunzione alla sommità | 0.40 | °C/W(1) |

| ψJB | Parametro di caratterizzazione giunzione-scheda | 32.0 | °C/W(1) |

(1) °C/W = gradi Celsius per watt.

8.9 Bande di frequenza RF

Oltre l'intervallo di temperature operative in aria libera (se non diversamente specificato).

| PARAMETRO | MINIMO | TIPO | Massimo | UNITÀ |

| Banda di frequenza | 863 | 930 | MHz |

8.10 Da 861 MHz a 1054 MHz – Ricezione (RX)

Quando misurato sul progetto di riferimento CC1312PSIP-EM con Tc = 25 °C, VDDS = 3.0 V con CC/CC abilitato e PA ad alta potenza collegato a VDDS se non diversamente specificato.

Tutte le misurazioni vengono eseguite all'ingresso dell'antenna con un percorso combinato RX e TX, ad eccezione del PA ad alta potenza che viene misurato su una connessione dell'antenna dedicata. Tutte le misurazioni vengono eseguite condotte.

|

PARAMETRO |

CONDIZIONI DI PROVA | MINIMO | TIPO | Massimo | UNITÀ |

|

Parametri generali |

|||||

| Larghezza di banda di ricezione programmabile per il filtro del canale digitale | 4 | 4000 | kHz | ||

| Dimensione del passo della velocità dati | 1.5 | punti | |||

| Emissioni spurie da 25 MHz a 1 GHz | 868 MHz Emissioni condotte misurate secondo ETSI EN 300 220 | < -57 | dBm | ||

| Emissioni spurie da 1 GHz a 13 GHz | < -47 | dBm | |||

| 802.15.4, 50 kbps, deviazione ±25 kHz, 2-GFSK, larghezza di banda RX 100 kHz | |||||

| Sensibilità | BER = 10–2, 868 MHz | –108 | dBm | ||

| Limite di saturazione | BER = 10–2, 868 MHz | 10 | dBm | ||

| Selettività, ±200 kHz | BER = 10–2 MHz(1) | 44 | dB | ||

| Selettività, ±400 kHz | BER = 10–2, 868 MHz(1) | 48 | dB | ||

| Blocco, ±1 MHz | BER = 10–2, 868 MHz(1) | 57 | dB | ||

| Blocco, ±2 MHz | BER = 10–2, 868 MHz(1) | 62 | dB | ||

| Blocco, ±5 MHz | BER = 10–2, 868 MHz(1) | 68 | dB | ||

| Blocco, ±10 MHz | BER = 10–2, 868 MHz(1) | 76 | dB | ||

| Rifiuto dell'immagine (compensazione dell'immagine abilitata) | BER = 10–2, 868 MHz(1) | 39 | dB | ||

| Gamma dinamica RSSI | A partire dal limite di sensibilità | 95 | dB | ||

| Precisione RSSI | A partire dal limite di sensibilità attraverso la gamma dinamica data | ±3 | dB | ||

| 802.15.4, 100 kbps, deviazione ±25 kHz, 2-GFSK, larghezza di banda RX 137 kHz | |||||

| Sensibilità 100 kbps | 868 MHz, 1% PER, carico utile di 127 byte | -101 | dBm | ||

| Selettività, ±200 kHz | 868 MHz, 1% PER, carico utile di 127 byte. Segnale ricercato a -96 dBm | 38 | dB | ||

| Selettività, ±400 kHz | 868 MHz, 1% PER, carico utile di 127 byte. Segnale ricercato a -96 dBm | 45 | dB | ||

| Rifiuto co-canale | 868 MHz, 1% PER, carico utile di 127 byte. Segnale ricercato a -79 dBm | -9 | dB | ||

| 802.15.4, 200 kbps, deviazione ±50 kHz, 2-GFSK, larghezza di banda RX 311 kHz | |||||

| Sensibilità | BER = 10–2, 868 MHz | –103 | dBm | ||

| Sensibilità | BER = 10–2, 915 MHz | –103 | dBm | ||

| Selettività, ±400 kHz | BER = 10–2, 915 MHz. Segnale desiderato 3 dB sopra il limite di sensibilità. | 41 | dB | ||

| Selettività, ±800 kHz | BER = 10–2, 915 MHz. Segnale desiderato 3 dB sopra il limite di sensibilità. | 47 | dB | ||

| Blocco, ±2 MHz | BER = 10–2, 915 MHz. Segnale desiderato 3 dB sopra il limite di sensibilità. | 55 | dB | ||

| Blocco, ±10 MHz | BER = 10–2, 915 MHz. Segnale desiderato 3 dB sopra il limite di sensibilità. | 67 | dB | ||

| 802.15.4, 500 kbps, deviazione ±190 kHz, 2-GFSK, larghezza di banda RX 655 kHz | |||||

| Sensibilità 500 kbps | 916 MHz, 1% PER, carico utile di 127 byte | -90 | dBm | ||

| Selettività, ±1 MHz | 916 MHz, 1% PER, carico utile di 127 byte. Segnale ricercato a -88 dBm | 11 | dB | ||

| Selettività, ±2 MHz | 916 MHz, 1% PER, carico utile di 127 byte. Segnale ricercato a -88 dBm | 43 | dB | ||

| Rifiuto co-canale | 916 MHz, 1% PER, carico utile di 127 byte. Segnale ricercato a -71 dBm | -9 | dB | ||

|

SimpleLink™ Long Range 2.5 kbps o 5 kbps (20 ksym/s, 2-GFSK, deviazione ±5 kHz, FEC (Half Rate), DSSS = 1:2 o 1:4, larghezza di banda RX 34 kHz |

|||||

| Sensibilità | 2.5 kbps, BER = 10–2, 868 MHz | -119 | dBm | ||

| Sensibilità | 5 kbps, BER = 10–2, 868 MHz | -117 | dBm | ||

| Limite di saturazione | 2.5 kbps, BER = 10–2, 868 MHz | 10 | dBm | ||

| Selettività, ±100 kHz | 2.5 kbps, BER = 10–2, 868 MHz(1) | 49 | dB | ||

| Selettività, ±200 kHz | 2.5 kbps, BER = 10–2, 868 MHz(1) | 50 | dB | ||

| Selettività, ±300 kHz | 2.5 kbps, BER = 10–2, 868 MHz(1) | 51 | dB | ||

| Blocco, ±1 MHz | 2.5 kbps, BER = 10–2, 868 MHz(1) | 63 | dB | ||

| Blocco, ±2 MHz | 2.5 kbps, BER = 10–2, 868 MHz(1) | 68 | dB | ||

| Blocco, ±5 MHz | 2.5 kbps, BER = 10–2, 868 MHz(1) | 78 | dB | ||

| Blocco, ±10 MHz | 2.5 kbps, BER = 10–2, 868 MHz(1) | 87 | dB | ||

Quando misurato sul progetto di riferimento CC1312PSIP-EM con Tc = 25 °C, VDDS = 3.0 V con CC/CC abilitato e PA ad alta potenza collegato a VDDS se non diversamente specificato.

Tutte le misurazioni vengono eseguite all'ingresso dell'antenna con un percorso combinato RX e TX, ad eccezione del PA ad alta potenza che viene misurato su una connessione dell'antenna dedicata. Tutte le misurazioni vengono eseguite condotte.

| PARAMETRO | CONDIZIONI DI PROVA | MIN TIPO MAX | UNITÀ |

| Rifiuto dell'immagine (compensazione dell'immagine abilitata) | 2.5 kbps, BER = 10–2, 868 MHz(1) | 45 | dB |

| Gamma dinamica RSSI | A partire dal limite di sensibilità | 97 | dB |

| Precisione RSSI | A partire dal limite di sensibilità attraverso la gamma dinamica data | ±3 | dB |

|

M-Bus wireless |

|||

| Sensibilità del ricevitore, modalità C wM-BUS, 100 kbps ±45 kHz | Larghezza di banda del ricevitore 236 kHz, BER 1% | -104 | dBm |

| Sensibilità del ricevitore, modalità T wM-BUS, 100 kbps ±50 kHz | Larghezza di banda del ricevitore 236 kHz, BER 1% | -103 | dBm |

| Sensibilità del ricevitore, modalità wM-BUS S2, 32.768 kbps ±50 kHz | Larghezza di banda del ricevitore 196 kHz, BER 1% | -109 | dBm |

| Sensibilità del ricevitore, modalità wM-BUS S1, 32.768 kbps ±50 kHz | Larghezza di banda del ricevitore 311 kHz, BER 1% | -107 | dBm |

|

OOK, 4.8 kbps, larghezza di banda RX 39 kHz |

|||

| Sensibilità | BER = 10–2, 868 MHz | -112 | dBm |

| Sensibilità | BER = 10–2, 915 MHz | -112 | dBm |

|

Banda stretta, deviazione ±9.6 kHz 2.4 kbps, 2-GFSK, 868 MHz, larghezza di banda RX 17.1 kHz |

|||

| Sensibilità | 1% BER | -118 | dBm |

| Rifiuto del canale adiacente | 1% BER. Segnale desiderato 3 dB sopra il limite di sensibilità di riferimento ETSI (-104.6 dBm). Interferente ±20 kHz | 39 | dB |

| Rifiuto del canale alternativo | 1% BER. Segnale desiderato 3 dB sopra il limite di sensibilità di riferimento ETSI (-104.6 dBm). Interferente ±40 kHz | 40 | dB |

| Blocco, ±1 MHz | 1% BER. Segnale desiderato 3 dB sopra il limite di sensibilità di riferimento ETSI (-104.6 dBm). | 65 | dB |

| Blocco, ±2 MHz | 69 | dB | |

| Blocco, ±10 MHz | 85 | dB | |

|

1 Mbps, deviazione ±350 kHz, 2-GFSK, larghezza di banda RX 2.2 MHz |

|||

| Sensibilità | BER = 10–2, 868 MHz | -94 | dBm |

| Sensibilità | BER = 10–2, 915 MHz | -93 | dBm |

| Blocco, +2 MHz | BER = 10–2, 915 MHz. Segnale desiderato 3 dB sopra il limite di sensibilità. | 44 | dB |

| Blocco, -2 MHz | BER = 10–2, 915 MHz. Segnale desiderato 3 dB sopra il limite di sensibilità. | 27 | dB |

| Blocco, +10 MHz | BER = 10–2, 915 MHz. Segnale desiderato 3 dB sopra il limite di sensibilità. | 59 | dB |

| Blocco, -10 MHz | BER = 10–2, 915 MHz. Segnale desiderato 3 dB sopra il limite di sensibilità. | 54 | dB |

|

Wi-SOLE, 2-GFSK |

|||

| Sensibilità | 50 kbps, deviazione ±12.5 kHz, 2-GFSK, 866.6 MHz, 68 kHz RX BW, 10% PER, carico utile 250 byte | -104 | dBm |

| Selettività, -100 kHz, 50 kbps, deviazione ±12.5 kHz, 2-GFSK, 866.6 MHz | 50 kbps, deviazione di ±12.5 kHz, 2-GFSK, larghezza di banda RX 68 kHz, 866.6 MHz, 10% PER, payload di 250 byte. Segnale desiderato 3 dB sopra il livello di sensibilità | 32 | dB |

| Selettività, +100 kHz, 50 kbps, deviazione ±12.5 kHz, 2-GFSK, 866.6 MHz | 33 | dB | |

| Selettività, ±100 kHz, 50 kbps, deviazione ±12.5 kHz, 2-GFSK, 866.6 MHz | 30 | dB | |

| Selettività, -200 kHz, 50 kbps, deviazione ±12.5 kHz, 2-GFSK, 866.6 MHz | 36 | dB | |

| Selettività, +200 kHz, 50 kbps, deviazione ±12.5 kHz, 2-GFSK, 866.6 MHz | 38 | dB | |

| Selettività, ±200 kHz, 50 kbps, deviazione ±12.5 kHz, 2-GFSK, 866.6 MHz | 37 | dB | |

| Sensibilità | 50 kbps, deviazione di ±25 kHz, 2-GFSK, larghezza di banda RX 98 kHz, 918.2 MHz, 10% PER, payload di 250 byte | -104 | dBm |

Quando misurato sul progetto di riferimento CC1312PSIP-EM con Tc = 25 °C, VDDS = 3.0 V con CC/CC abilitato e PA ad alta potenza collegato a VDDS se non diversamente specificato. Tutte le misurazioni vengono eseguite all'ingresso dell'antenna con un percorso RX e TX combinato, ad eccezione del PA ad alta potenza che viene misurato su una connessione dell'antenna dedicata. Tutte le misurazioni vengono eseguite condotte.

| PARAMETRO | CONDIZIONI DI PROVA | MIN TIPO MAX |

UNITÀ |

| Selettività, -200 kHz, 50 kbps, deviazione ±25 kHz, 2-GFSK, 918.2 MHz | 50 kbps, deviazione di ±25 kHz, 2-GFSK, larghezza di banda RX 98 kHz, 918.2 MHz, 10% PER, payload di 250 byte. Segnale desiderato 3 dB sopra il livello di sensibilità | 34 | dB |

| Selettività, +200 kHz, 50 kbps, deviazione ±25 kHz, 2-GFSK, 918.2 MHz | 35 | dB | |

| Selettività, ±200 kHz, 50 kbps, deviazione ±25 kHz, 2-GFSK, 918.2 MHz | 34 | dB | |

| Selettività, -400 kHz, 50 kbps, deviazione ±25 kHz, 2-GFSK, 918.2 MHz | 40 | dB | |

| Selettività, +400 kHz, 50 kbps, deviazione ±25 kHz, 2-GFSK, 918.2 MHz | 40 | dB | |

| Selettività, ±400 kHz, 50 kbps, deviazione ±25 kHz, 2-GFSK, 918.2 MHz | 40 | dB | |

| Sensibilità | 100 kbps, deviazione di ±25 kHz, 2-GFSK, 866.6 MHz, 135 kHz RX BW, 10% PER, payload di 250 byte | -102 | dBm |

| Sensibilità | 100 kbps, deviazione di ±25 kHz, 2-GFSK, 918.2 MHz, 135 kHz RX BW, 10% PER, payload di 250 byte | -101 | dBm |

| Selettività, -200 kHz, 100 kbps, deviazione ±25 kHz, 2-GFSK, 866.6 MHz | 100 kbps, deviazione di ±25 kHz, 2-GFSK, larghezza di banda RX 135 kHz, 866.6 MHz, 10% PER, payload di 250 byte. Segnale desiderato 3 dB sopra il livello di sensibilità | 37 | dB |

| Selettività, +200 kHz, 100 kbps, deviazione ±25 kHz, 2-GFSK, 866.6 MHz | 38 | dB | |

| Selettività, ±200 kHz, 100 kbps, deviazione ±25 kHz, 2-GFSK, 866.6 MHz | 37 | dB | |

| Selettività, -400 kHz, 100 kbps, deviazione ±25 kHz, 2-GFSK, 866.6 MHz | 45 | dB | |

| Selettività, +400 kHz, 100 kbps, deviazione ±25 kHz, 2-GFSK, 866.6 MHz | 45 | dB | |

| Selettività, ±400 kHz, 100 kbps, deviazione ±25 kHz, 2-GFSK, 866.6 MHz | 45 | dB | |

| Sensibilità | 100 kbps, deviazione di ±50 kHz, 2-GFSK, 920.9 MHz, 196 kHz RX BW, 10% PER, payload di 250 byte | -100 | dBm |

| Selettività, -400 kHz, 100 kbps, deviazione ±50 kHz, 2-GFSK, 920.9 MHz | 100 kbps, deviazione di ±50 kHz, 2-GFSK, larghezza di banda RX 196 kHz, 920.9 MHz, 10% PER, payload di 250 byte. Segnale desiderato 3 dB sopra il livello di sensibilità | 40 | dB |

| Selettività, +400 kHz, 100 kbps, deviazione ±50 kHz, 2-GFSK, 920.9 MHz | 40 | dB | |

| Selettività, ±400 kHz, 100 kbps, deviazione ±50 kHz, 2-GFSK, 920.9 MHz | 40 | dB | |

| Selettività, -800 kHz, 100 kbps, deviazione ±50 kHz, 2-GFSK, 920.9 MHz | 46 | dB | |

| Selettività, +800 kHz, 100 kbps, deviazione ±50 kHz, 2-GFSK, 920.9 MHz | 52 | dB | |

| Selettività, ±800 kHz, 100 kbps, deviazione ±50 kHz, 2-GFSK, 920.9 MHz | 48 | dB | |

| Sensibilità | 150 kbps, deviazione di ±37.5 kHz, 2-GFSK, 918.4 MHz, 273 kHz RX BW, 10% PER, payload di 250 byte | -96 | dBm |

| Selettività, -400 kHz, 150 kbps, deviazione ±37.5 kHz, 2-GFSK, 918.4 MHz | 150 kbps, deviazione di ±37.5 kHz, 2-GFSK, larghezza di banda RX 273 kHz, 918.4 MHz, 10% PER, payload di 250 byte. Segnale desiderato 3 dB sopra il livello di sensibilità | 41 | dB |

| Selettività, +400 kHz, 150 kbps, deviazione ±37.5 kHz, 2-GFSK, 918.4 MHz | 42 | dB | |

| Selettività, -800 kHz, 150 kbps, deviazione ±37.5 kHz, 2-GFSK, 918.4 MHz | 46 | dB | |

| Selettività, +800 kHz, 150 kbps, deviazione ±37.5 kHz, 2-GFSK, 918.4 MHz | 49 | dB | |

| Sensibilità | -96 | dBm |

Quando misurato sul progetto di riferimento CC1312PSIP-EM con Tc = 25 °C, VDDS = 3.0 V con CC/CC abilitato e PA ad alta potenza collegato a VDDS se non diversamente specificato.

Tutte le misurazioni vengono eseguite all'ingresso dell'antenna con un percorso combinato RX e TX, ad eccezione del PA ad alta potenza che viene misurato su una connessione dell'antenna dedicata. Tutte le misurazioni vengono eseguite condotte.

| PARAMETRO | CONDIZIONI DI PROVA | MIN TIPO MAX |

UNITÀ |

| Selettività, -400 kHz, 150 kbps, deviazione ±37.5 kHz, 2-GFSK, 920.9 MHz | 150 kbps, deviazione di ±37.5 kHz, 2-GFSK, larghezza di banda RX 273 kHz, 920.9 MHz, 10% PER, payload di 250 byte. Segnale desiderato 3 dB sopra il livello di sensibilità | 40 | dB |

| Selettività, +400 kHz, 150 kbps, deviazione ±37.5 kHz, 2-GFSK, 920.9 MHz | 42 | dB | |

| Selettività, ±400 kHz, 150 kbps, deviazione ±37.5 kHz, 2-GFSK, 920.9 MHz | 40 | dB | |

| Selettività, -800 kHz, 150 kbps, deviazione ±37.5 kHz, 2-GFSK, 920.9 MHz | 46 | dB | |

| Selettività, +800 kHz, 150 kbps, deviazione ±37.5 kHz, 2-GFSK, 920.9 MHz | 49 | dB | |

| Selettività, ±800 kHz, 150 kbps, deviazione ±37.5 kHz, 2-GFSK, 920.9 MHz | 46 | dB | |

| Sensibilità | 200 kbps, deviazione di ±50 kHz, 2-GFSK, 918.4 MHz, 273 kHz RX BW, 10% PER, payload di 250 byte | -97 | dBm |

| Selettività, -400 kHz, 200 kbps, deviazione ±50 kHz, 2-GFSK, 918.4 MHz | 200 kbps, deviazione di ±50 kHz, 2-GFSK, larghezza di banda RX 273 kHz, 918.4 MHz, 10% PER, payload di 250 byte. Segnale desiderato 3 dB sopra il livello di sensibilità | 40 | dB |

| Selettività, +400 kHz, 200 kbps, deviazione ±50 kHz, 2-GFSK, 918.4 MHz | 43 | dB | |

| Selettività, ±400 kHz, 200 kbps, deviazione ±50 kHz, 2-GFSK, 918.4 MHz | 41 | dB | |

| Selettività, -800 kHz, 200 kbps, deviazione ±50 kHz, 2-GFSK, 918.4 MHz | 46 | dB | |

| Selettività, +800 kHz, 200 kbps, deviazione ±50 kHz, 2-GFSK, 918.4 MHz | 50 | dB | |

| Selettività, ±800 kHz, 200 kbps, deviazione ±50 kHz, 2-GFSK, 918.4 MHz | 48 | dB | |

| Sensibilità | 200 kbps, deviazione di ±100 kHz, 2-GFSK, 920.8 MHz, 273 kHz RX BW, 10% PER, payload di 250 byte | -96 | dBm |

| Selettività, -600 kHz, 200 kbps, deviazione ±100 kHz, 2-GFSK, 920.8 MHz | 200 kbps, deviazione di ±100 kHz, 2-GFSK, larghezza di banda RX 273 kHz, 920.8 MHz, 10% PER, payload di 250 byte. Segnale desiderato 3 dB sopra il livello di sensibilità | 43 | dB |

| Selettività, +600 kHz, 200 kbps, deviazione ±100 kHz, 2-GFSK, 920.8 MHz | 47 | dB | |

| Selettività, ±600 kHz, 200 kbps, deviazione ±100 kHz, 2-GFSK, 920.8 MHz | 44 | dB | |

| Selettività, -1200 kHz, 200 kbps, deviazione ±100 kHz, 2-GFSK, 920.8 MHz | 51 | dB | |

| Selettività, +1200 kHz, 200 kbps, deviazione ±100 kHz, 2-GFSK, 920.8 MHz | 54 | dB | |

| Selettività, ±1200 kHz, 200 kbps, deviazione ±100 kHz, 2-GFSK, 920.8 MHz | 51 | dB | |

| Sensibilità | 300 kbps, deviazione di ±75 kHz, 2-GFSK, 917.6 MHz, 576 kHz RX BW, 10% PER, payload di 250 byte | -94 | dBm |

| Selettività, -600 kHz, 300 kbps, deviazione ±75 kHz, 2-GFSK, 917.6 MHz | 300 kbps, deviazione di ±75 kHz, 2-GFSK, larghezza di banda RX 576 kHz, 917.6 MHz, 10% PER, payload di 250 byte. Segnale desiderato 3 dB sopra il livello di sensibilità | 27 | dB |

| Selettività, +600 kHz, 300 kbps, deviazione ±75 kHz, 2-GFSK, 917.6 MHz | 45 | dB | |

| Selettività, ±600 kHz, 300 kbps, deviazione ±75 kHz, 2-GFSK, 917.6 MHz | 35 | dB | |

| Selettività, -1200 kHz, 300 kbps, deviazione ±75 kHz, 2-GFSK, 917.6 MHz | 46 | dB | |

| Selettività, +1200 kHz, 300 kbps, deviazione ±75 kHz, 2-GFSK, 920.8 MHz | 50 | dB | |

| Selettività, ±1200 kHz, 300 kbps, deviazione ±75 kHz, 2-GFSK, 917.6 MHz | 48 | dB | |

|

WB-DSSS, 240/120/60/30 kbps (480 ksim/s, 2-GFSK, deviazione ±195 kHz, FEC (metà velocità), DSSS = 1/2/4/8, 622 kHz RX BW) |

|||

| Sensibilità | 240 kbps, DSSS = 1, BER = 10–2, 915 MHz | -101 | dBm |

| Sensibilità | 120 kbps, DSSS = 2, BER = 10–2, 915 MHz | -103 | dBm |

Quando misurato sul progetto di riferimento CC1312PSIP-EM con Tc = 25 °C, VDDS = 3.0 V con CC/CC abilitato e PA ad alta potenza collegato a VDDS se non diversamente specificato.

Tutte le misurazioni vengono eseguite all'ingresso dell'antenna con un percorso combinato RX e TX, ad eccezione del PA ad alta potenza che viene misurato su una connessione dell'antenna dedicata. Tutte le misurazioni vengono eseguite condotte.

| PARAMETRO | CONDIZIONI DI PROVA | MIN TIPO MAX |

UNITÀ |

| Sensibilità | 60 kbps, DSSS = 4, BER = 10–2, 915 MHz | -105 | dBm |

| Sensibilità | 30 kbps, DSSS = 8, BER = 10–2, 915 MHz | -106 | dBm |

| Blocco ±1 MHz | 240 kbps, DSSS = 1, BER = 10–2, 915 MHz | 49 | dB |

| Blocco ±2 MHz | 240 kbps, DSSS = 1, BER = 10–2, 915 MHz | 53 | dB |

| Blocco ±5 MHz | 240 kbps, DSSS = 1, BER = 10–2, 915 MHz | 58 | dB |

| Blocco ±10 MHz | 240 kbps, DSSS = 1, BER = 10–2, 915 MHz | 67 | dB |

(1) Segnale desiderato 3 dB sopra il limite di sensibilità di riferimento secondo ETSI EN 300 220 v. 3.1.1

8.11 Da 861 MHz a 1054 MHz – Trasmissione (TX)

Misurato sul progetto di riferimento CC1312PSIP-EM con Tc = 25 °C, VDDS = 3.0 V con CC/CC abilitato e PA ad alta potenza collegato a VDDS utilizzando 2-GFSK, 50 kbps, deviazione di ±25 kHz se non diversamente specificato. Tutte le misurazioni vengono eseguite all'ingresso dell'antenna con un percorso RX e TX combinato, ad eccezione del PA ad alta potenza che viene misurato su una connessione dell'antenna dedicata. Tutte le misurazioni vengono eseguite condotte. (1) c

|

PARAMETRO |

CONDIZIONI DI PROVA | MINIMO | TIPO | Massimo |

UNITÀ |

|

|

Parametri generali |

||||||

| Potenza di uscita massima, modalità boost PA normale | VDDR = 1.95 V Vol. alimentazione minimotage (VDDS) per la modalità boost è 2.1 V 915 MHz | 14 | dBm | |||

| Potenza di uscita massima, PA normale | 868 MHz e 915 MHz | 12.4 | dBm | |||

| Intervallo programmabile della potenza di uscita PA normale | 868 MHz e 915 MHz | 34 | dB | |||

| Variazione della potenza in uscita in base alla temperatura PA normale | Impostazione +10 dBm Superamento dell'intervallo di temperatura operativa consigliato | ±2 | dB | |||

| Variazione della potenza di uscita in base alla temperatura Modalità Boost, PA normale | Impostazione +14 dBm Superamento dell'intervallo di temperatura operativa consigliato | ±1.5 | dB | |||

|

Emissioni spurie e armoniche |

||||||

| Emissioni spurie (armoniche escluse) PA normale (2) | Da 30 MHz a 1 GHz | +14 dBm impostazione bande limitate ETSI | < -54 | dBm | ||

| Impostazione +14 dBm ETSI al di fuori delle bande limitate | < -36 | dBm | ||||

| Da 1 GHz a 12.75 GHz (fuori dalle bande limitate ETSI) | Impostazione +14 dBm misurata nella larghezza di banda di 1 MHz (ETSI) | < -30 | -35 | dBm | ||

| Emissioni spurie fuori banda PA normale, 915 MHz (2) | Da 30 MHz a 88 MHz (all'interno delle bande limitate FCC) | Impostazione +14 dBm | < -56 | dBm | ||

| Da 88 MHz a 216 MHz (all'interno delle bande limitate FCC) | Impostazione +14 dBm | < -52 | dBm | |||

| Da 216 MHz a 960 MHz (all'interno delle bande limitate FCC) | Impostazione +14 dBm | < -50 | dBm | |||

| Da 960 MHz a 2390 MHz e oltre 2483.5 MHz (all'interno della banda limitata FCC) | Impostazione +14 dBm | <-42 | dBm | |||

| Da 1 GHz a 12.75 GHz (fuori dalle bande limitate FCC) | Impostazione +14 dBm | < -40 | -44 | dBm | ||

| Emissioni spurie fuori banda PA normale, 920.6/928 MHz (2) | Sotto i 710 MHz (ARIB T-108) | Impostazione +14 dBm | < -36 | dBm | ||

| Da 710 MHz a 900 MHz (ARIB T-108) | Impostazione +14 dBm | < -55 | dBm | |||

| Da 900 MHz a 915 MHz (ARIB T-108) | Impostazione +14 dBm | < -55 | dBm | |||

| Da 930 MHz a 1000 MHz (ARIB T-108) | Impostazione +14 dBm | < -55 | dBm | |||

| Da 1000 MHz a 1215 MHz (ARIB T-108) | Impostazione +14 dBm | < -45 | dBm | |||

| Sopra 1215 MHz (ARIB T-108) | Impostazione +14 dBm | < -30 | dBm | |||

| Armoniche PA regolare | Seconda armonica | Impostazione +14 dBm, 868 MHz | < -30 | dBm | ||

| Impostazione +14 dBm, 915 MHz | < -30 | |||||

| Terza armonica | Impostazione +14 dBm, 868 MHz | < -30 | dBm | |||

| Impostazione +14 dBm, 915 MHz | < -42 | |||||

| Quarta armonica | Impostazione +14 dBm, 868 MHz | < -30 | dBm | |||

| Impostazione +14 dBm, 915 MHz | < -30 | |||||

| Quinta armonica | Impostazione +14 dBm, 868 MHz | < -30 | dBm | |||

| Impostazione +14 dBm, 915 MHz | < -42 | |||||

Misurato sul progetto di riferimento CC1312PSIP-EM con Tc = 25 °C, VDDS = 3.0 V con CC/CC abilitato e PA ad alta potenza collegato a VDDS utilizzando 2-GFSK, 50 kbps, deviazione di ±25 kHz se non diversamente specificato. Tutte le misurazioni vengono eseguite all'ingresso dell'antenna con un percorso combinato RX e TX, ad eccezione del PA ad alta potenza che viene misurato su una connessione dell'antenna dedicata. Tutte le misurazioni vengono eseguite condotte.(1)

| PARAMETRO | CONDIZIONI DI PROVA | MIN TIPO MAX |

UNITÀ |

|

|

Potenza del canale adiacente |

||||

| Potenza del canale adiacente, PA normale da 14 dBm | Canale adiacente, offset 20 kHz. 9.6 kbps, h=0.5 | Impostazione 12.5 dBm. 868.3 MHz. Canale 14 kHz in bianco e nero | -24 | dBm |

| Potenza del canale alternativo, PA normale da 14 dBm | Canale alternativo, offset 40 kHz. 9.6 kbps, h=0.5 | Impostazione 12.5 dBm. 868.3 MHz. Canale 14 kHz in bianco e nero | -31 | dBm |

(1) Alcune combinazioni di frequenza, velocità dati e formato di modulazione richiedono l'uso di condensatori di carico a cristallo esterni per la conformità normativa. Maggiori dettagli possono essere trovati negli errata del dispositivo.

(2) Adatto per sistemi mirati alla conformità con EN 300 220, EN 303 131, EN 303 204, FCC CFR47 Parte 15, ARIB STD-T108.

8.12 Da 861 MHz a 1054 MHz – Modalità a banda larga con rumore di fase PLL

Se misurato sul progetto di riferimento con Tc = 25 °C, VDDS = 3.0 V.

| PARAMETRO | CONDIZIONI DI PROVA | MINIMO | TIPO | Massimo |

UNITÀ |

| Rumore di fase nelle bande 868 e 915 MHz. Larghezza di banda del loop PLL da 20 kHz | Scostamento di ±10kHz | –74 | dBc/Hz | ||

| Scostamento di ±100kHz | –97 | dBc/Hz | |||

| Scostamento di ±200kHz | –107 | dBc/Hz | |||

| Scostamento di ±400kHz | –113 | dBc/Hz | |||

| Scostamento di ±1000kHz | –120 | dBc/Hz | |||

| Scostamento di ±2000kHz | –127 | dBc/Hz | |||

| Scostamento di ±10000kHz | –141 | dBc/Hz | |||

8.13 Da 861 MHz a 1054 MHz – Modalità a banda stretta con rumore di fase PLL

Se misurato sul progetto di riferimento con Tc = 25 °C, VDDS = 3.0 V.

| PARAMETRO | CONDIZIONI DI PROVA | MINIMO | TIPO | Massimo |

UNITÀ |

| Rumore di fase nelle bande 868 e 915 MHz Banda loop PLL da 150 kHz con | Scostamento di ±10kHz | –93 | dBc/Hz | ||

| Scostamento di ±100kHz | –93 | dBc/Hz | |||

| Scostamento di ±200kHz | –95 | dBc/Hz | |||

| Scostamento di ±400kHz | –104 | dBc/Hz | |||

| Scostamento di ±1000kHz | –121 | dBc/Hz | |||

| Scostamento di ±2000kHz | –130 | dBc/Hz | |||

| Scostamento di ±10000kHz | –140 | dBc/Hz | |||

8.14 Caratteristiche di temporizzazione e commutazione

8.14.1 Tempi di ripristino

| PARAMETRO | MINIMO | TIPO | Massimo |

UNITÀ |

| RESET_N durata bassa | 1 | ms | ||

8.14.2 Orario di sveglia

Misurato sulla temperatura operativa in aria libera con VDDS = 3.0 V (se non diversamente specificato). I tempi qui elencati non includono il sovraccarico del software.

| PARAMETRO | CONDIZIONI DI PROVA | MINIMO | TIPO | Massimo | UNITÀ |

| MCU, ripristinato su attivo(1) | 850 – 4000 | ms | |||

| MCU, spegnimento su attivo(1) | 850 – 4000 | ms | |||

| MCU, da standby ad attivo | 165 | ms | |||

| MCU, da attivo a standby | 39 | ms | |||

Misurato sulla temperatura operativa in aria libera con VDDS = 3.0 V (se non diversamente specificato). I tempi qui elencati non includono il sovraccarico del software.

| PARAMETRO | CONDIZIONI DI PROVA | MIN TIPO MAX |

UNITÀ |

| MCU, da inattivo ad attivo | 15 | ms |

(1) Il tempo di riattivazione dipende dalla carica rimanente sul condensatore VDDR all'avvio del dispositivo e quindi da quanto tempo il dispositivo è rimasto in modalità Ripristino o Spegnimento prima di riavviarsi. Il tempo di riattivazione aumenta con un valore del condensatore più elevato.

8.14.3 Specifiche dell'orologio

8.14.3.1 Oscillatore a cristallo da 48 MHz (XOSC_HF) e precisione della frequenza RF

Il modulo contiene un cristallo da 48 MHz collegato all'oscillatore. Durante il test di produzione del modulo, la serie di condensatori interni che caricano il cristallo viene regolata per ridurre al minimo l'errore di frequenza del cristallo. Il test di produzione riduce inoltre al minimo l'errore di frequenza RF a temperatura ambiente regolando la parola di frequenza RF (PLL). Questa correzione iniziale della frequenza RF viene utilizzata nel software (se abilitato) per compensare la frequenza RF in base alla deriva termica stimata del cristallo. Misurato su un progetto di riferimento Texas Instruments con Tc = 25 °C, VDDS = 3.0 V, se non diversamente specificato.

|

|

PARAMETRO | MINIMO | TIPO | Massimo |

UNITÀ |

| Frequenza di cristallo | 48 | MHz | |||

| Tempo di avvio dell'oscillatore al cristallo(2) | 200 | ms | |||

| Precisione della frequenza iniziale di 48 MHz a 25° | -5 | 2 | 5 | parti per milione | |

| Stabilità di frequenza a 48 MHz, deriva termica da -40° a 105° | -16 | 18 | parti per milione | ||

| Invecchiamento in cristallo, 5 anni | -2 | 2 | parti per milione | ||

| Invecchiamento in cristallo, 10 anni | -4 | 2 | parti per milione | ||

| Precisione della frequenza RF inclusa la deriva termica compensata dal software interno, escluso l'invecchiamento, da -40° a 65°. Basato sulla deriva stimata dei cristalli rispetto alla temperatura in base alle specifiche dei cristalli del produttore. | -10 | 10 | parti per milione | ||

- Sondare o fermare in altro modo il cristallo mentre il convertitore DC/DC è abilitato può causare danni permanenti al dispositivo.

- Tempo di avvio utilizzando il driver di alimentazione fornito da TI. Il tempo di avvio può aumentare se il driver non viene utilizzato.

8.14.3.2 Oscillatore RC da 48 MHz (RCOSC_HF)

Misurato su un progetto di riferimento Texas Instruments con Tc = 25 °C, VDDS = 3.0 V, se non diversamente specificato.

| MINIMO | TIPO | Massimo |

UNITÀ |

|

| Frequenza | 48 | MHz | ||

| Precisione della frequenza non calibrata | ±1 | % | ||

| Precisione della frequenza calibrata(1) | ±0.25 | % | ||

| Tempo di avvio | 5 | ms | ||

- Precisione relativa alla sorgente di calibrazione (XOSC_HF)

8.14.3.3 Oscillatore RC da 2 MHz (RCOSC_MF)

Misurato su un progetto di riferimento Texas Instruments con Tc = 25 °C, VDDS = 3.0 V, se non diversamente specificato.

| MINIMO | TIPO | Massimo | UNITÀ | |

| Frequenza calibrata | 2 | MHz | ||

| Tempo di avvio | 5 | ms | ||

8.14.3.4 Oscillatore a cristallo da 32.768 kHz (XOSC_LF) e precisione RTC

Il modulo contiene un cristallo da 32 kHz collegato all'oscillatore. Durante il test di produzione del modulo, l'RTC (Real Time Clock) derivato dall'oscillatore al cristallo da 32 kHz viene calibrato a temperatura ambiente. Questo viene fatto per ridurre al minimo l'errore RTC causato dall'errore iniziale del cristallo da 32 kHz. Questa correzione iniziale dell'RTC viene utilizzata nel software (se abilitato) per compensare l'RTC in base alla deriva termica stimata del cristallo. Misurato su un progetto di riferimento Texas Instruments con Tc = 25 °C, VDDS = 3.0 V, se non diversamente specificato.

|

|

MINIMO | TIPO | Massimo |

UNITÀ |

|

| Frequenza di cristallo | 32.768 | kHz | |||

| Precisione della frequenza iniziale a 25° | -20 | 20 | parti per milione | ||

| Invecchiamento del cristallo a 32kHz, primo anno | -3 | 3 | parti per milione | ||

| Precisione dell'orologio in tempo reale (RTC) utilizzando la compensazione della temperatura per il xtal a 32kHz (se abilitato nel software), escluso l'invecchiamento, da -40° a 105° gradi. Basato sulla deriva stimata dei cristalli rispetto alla temperatura in base alle specifiche dei cristalli del produttore. | -100 | 50 | parti per milione | ||

| Precisione dell'orologio in tempo reale (RTC) utilizzando la compensazione della temperatura per il xtal a 32kHz (se abilitato nel software), escluso l'invecchiamento, da -40° a 65° gradi. Basato sulla deriva stimata dei cristalli rispetto alla temperatura in base alle specifiche dei cristalli del produttore. | -50 | 50 | parti per milione | ||

8.14.3.5 Oscillatore RC da 32 kHz (RCOSC_LF)

Misurato su un progetto di riferimento Texas Instruments con Tc = 25 °C, VDDS = 3.0 V, se non diversamente specificato.

| MINIMO | TIPO | Massimo |

UNITÀ |

||

| Frequenza | 32.8 | kHz | |||

| RTC calibrato variazione(1) |

Calibrato periodicamente rispetto a XOSC_HF(2) | ±600(3) | parti per milione | ||

| Coefficiente di temperatura | 50 | ppm/°C | |||

- Quando si utilizza RCOSC_LF come sorgente per l'orologio di sistema a bassa frequenza (SCLK_LF), la precisione dell'orologio in tempo reale (RTC) derivato da SCLK_LF può essere migliorata misurando RCOSC_LF rispetto a XOSC_HF e compensando la velocità di tick dell'RTC. Questa funzionalità è disponibile tramite il driver Power fornito da TI.

- Il software del driver TI calibra l'RTC ogni volta che XOSC_HF è abilitato.

- La variazione di alcuni dispositivi può superare i 1000 ppm. Un'ulteriore calibrazione non migliorerà la variazione.

8.14.4 Caratteristiche dell'interfaccia seriale sincrona (SSI).

8.14.4.1.1 Caratteristiche dell'interfaccia seriale sincrona (SSI). oltre l'intervallo di temperature operative in aria libera (se non diversamente specificato)

8.14.4.1.1 Caratteristiche dell'interfaccia seriale sincrona (SSI). oltre l'intervallo di temperature operative in aria libera (se non diversamente specificato)

| PARAMETRO NO. | PARAMETRO | MINIMO | TIPO | Massimo | UNITÀ | |

| S1 | tclk_per | Tempo di ciclo SSIClk | 12 | 65024 | Orologi di sistema (2) | |

| S2 (1) | tclk_high | SSIClk è giunto il momento | 0.5 | tclk_per | ||

| S3(1) | tclk_low | SSIClk tempo basso | 0.5 | tclk_per | ||

- Fare riferimento ai diagrammi temporali SSI e .

- Quando si utilizza il driver di alimentazione fornito da TI, l'orologio del sistema SSI è sempre 48 MHz.

8.14.5UART

8.14.5.1 Caratteristiche UART

oltre l'intervallo di temperature operative in aria libera (se non diversamente specificato)

| PARAMETRO | MINIMO | TIPO | Massimo | UNITÀ |

| Tasso UART | 3 | MBaud | ||

8.15 Caratteristiche periferiche

8.15.1 ADC

8.15.1.1 Caratteristiche del convertitore analogico-digitale (ADC).

Tc = 25 °C, VDDS = 3.0 V e voltage ridimensionamento abilitato, se non diversamente specificato. (1)

I numeri relativi alle prestazioni richiedono l'uso di regolazioni di offset e guadagno nel software da parte dei driver ADC forniti da TI.

| PARAMETRO | CONDIZIONI DI PROVA | MINIMO | TIPO | Massimo |

UNITÀ |

|

| Ingresso voltage gamma | 0 | VDD | V | |||

| Risoluzione | 12 | Pezzi | ||||

| Sampla tariffa | 200 | ksps | ||||

| Offset | Riferimento interno equivalente a 4.3 V(2) | ±2 | LSB | |||

| Guadagna errore | Riferimento interno equivalente a 4.3 V(2) | ±7 | LSB | |||

| DNL(4) | Nonlinearità differenziale | >–1 | LSB | |||

| INLANDESE | Nonlinearità integrale | ±4 | LSB | |||

| ENOB | Numero effettivo di bit | Riferimento interno equivalente a 4.3 V(2), 200 kSampmeno, Tono di ingresso a 9.6 kHz |

9.8 | Pezzi | ||

| Riferimento interno equivalente a 4.3 V(2), 200 kSampmeno, Tono di ingresso a 9.6 kHz, CC/CC abilitato |

9.8 | |||||

| VDDS come riferimento, 200 kSamples/s, tono di ingresso a 9.6 kHz | 10.1 | |||||

| Riferimento interno, voltage ridimensionamento disabilitato, Anno 32amples media, 200 kSamples/s, tono di ingresso a 300 Hz |

11.1 | |||||

| Riferimento interno, voltage ridimensionamento disabilitato, modalità a 14 bit, 200 kSamples/s, tono di ingresso a 600 Hz (5) | 11.3 | |||||

| Riferimento interno, voltagRidimensionamento e disattivato, modalità a 15 bit, 200 kSamples/s, tono di ingresso a 150 Hz (5) | 11.6 | |||||

| THD | Distorsione armonica totale | Riferimento interno equivalente a 4.3 V(2), 200 kSamples/s, tono di ingresso a 9.6 kHz | –65 | dB | ||

| VDDS come riferimento, 200 kSamples/s, tono di ingresso a 9.6 kHz | –70 | |||||

| Riferimento interno, voltage ridimensionamento disabilitato, 32 samples media, 200 kSamples/s, tono di ingresso a 300 Hz | –72 | |||||

| SINAD, SNDR | Rapporto segnale-rumore e distorsione | Riferimento interno equivalente a 4.3 V(2), 200 kSamples/s, tono di ingresso a 9.6 kHz | 60 | dB | ||

| VDDS come riferimento, 200 kSamples/s, tono di ingresso a 9.6 kHz | 63 | |||||

| Riferimento interno, voltage ridimensionamento disabilitato, 32 samples media, 200 kSamples/s, tono di ingresso a 300 Hz | 68 | |||||

| SFDR | Gamma dinamica priva di spurie | Riferimento interno equivalente a 4.3 V(2), 200 kSamples/s, tono di ingresso a 9.6 kHz | 70 | dB | ||

| VDDS come riferimento, 200 kSamples/s, tono di ingresso a 9.6 kHz | 73 | |||||

| Riferimento interno, voltage ridimensionamento disabilitato, 32 samples media, 200 kSamples/s, tono di ingresso a 300 Hz | 75 | |||||

| Tempo di conversione | Conversione seriale, tempo in uscita, orologio da 24 MHz | 50 | Cicli dell'orologio | |||

| Consumo attuale | Riferimento interno equivalente a 4.3 V(2) | 0.40 | mA | |||

| Consumo attuale | VDDS come riferimento | 0.57 | mA | |||

| Riferimento voltage | Riferimento interno fisso equivalente (ingresso voltage ridimensionamento abilitato). Per la massima precisione, la conversione ADC deve essere avviata tramite l'API TI-RTOS per includere i fattori di compensazione guadagno/offset memorizzati in FCFG1 | 4.3(2) (3) | V | |||

| Riferimento voltage | Riferimento interno fisso (ingresso voltage ridimensionamento disabilitato). Per la massima precisione, la conversione ADC deve essere avviata tramite l'API TI-RTOS per includere i fattori di compensazione guadagno/offset memorizzati in FCFG1. Questo valore deriva dal valore scalato (4.3 V) come segue: Vriferimento = 4.3 V × 1408/4095 | 1.48 | V | |||

| Riferimento voltage | VDDS come riferimento, input voltage ridimensionamento abilitato | VDD | V | |||

| Riferimento voltage | VDDS come riferimento, input voltage ridimensionamento disabilitato | VDD / 2.82(3) | V | |||

Tc = 25 °C, VDDS = 3.0 V e voltage ridimensionamento abilitato, se non diversamente specificato. (1)

I numeri relativi alle prestazioni richiedono l'uso di regolazioni di offset e guadagno nel software da parte dei driver ADC forniti da TI.

| PARAMETRO | CONDIZIONI DI PROVA | MIN TIPO MAX |

UNITÀ |

|

| Impedenza di ingresso | 200 kSamples/s, voltage ridimensionamento abilitato. Ingresso capacitivo, l'impedenza di ingresso dipende da sampfrequenza ling e sampling tempo | >1 | MΩ | |

- Utilizzo dello standard IEEE 1241-2010 per la terminologia e i metodi di test

- Segnale di ingresso ridimensionato internamente prima della conversione, come se voltagL'intervallo era compreso tra 0 e 4.3 V

- Volume applicatotage deve rientrare sempre nei limiti massimi assoluti

- Nessun codice mancante

- Uscita_ADC = Σ(4 n samples ) >> n, n = bit extra desiderati

8.15.2 DAC

8.15.2.1 Caratteristiche del convertitore digitale-analogico (DAC).

Tc = 25 °C, VDDS = 3.0 V, se non diversamente specificato.

|

PARAMETRO |

CONDIZIONI DI PROVA | MINIMO | TIPO | Massimo | UNITÀ | |

|

Parametri generali |

||||||

| Risoluzione | 8 | Pezzi | ||||

|

VDD |

Volume di fornituratage | Qualsiasi carico, qualsiasi VRIF., precarica disattivata, pompa di carica DAC attivata | 1.8 | 3.8 |

V |

|

| Carico esterno(4), qualsiasi VRIF., precarica disattivata, pompa di carica DAC disattivata | 2.0 | 3.8 | ||||

| Qualsiasi carico, VRIF. = DCOUPL, precarica ON | 2.6 | 3.8 | ||||

| FDAC | Frequenza di clock | Buffer ON (consigliato per carico esterno) | 16 | 250 |

kHz |

|

| Buffer OFF (carico interno) | 16 | 1000 | ||||

| VoltagIl tempo di assestamento dell'uscita | VRIF. = VDDS, buffer OFF, carico interno | 13 | 1 / EDAC | |||

| VRIF. = VDDS, buffer ON, carico capacitivo esterno = 20 pF(3) | 13.8 | |||||

| Carico capacitivo esterno | 20 | 200 | pF | |||

| Carico resistivo esterno | 10 | MΩ | ||||

| Corrente di cortocircuito | 400 | µA | ||||

| ZMAX | Impedenza massima di uscita Vref = VDDS, buffer ON, CLK 250 kHz | VDDS = 3.8 V, pompa di carica DAC disattivata | 50.8 | kΩ | ||

| VDDS = 3.0 V, pompa di carica DAC accesa | 51.7 | |||||

| VDDS = 3.0 V, pompa di carica DAC disattivata | 53.2 | |||||

| VDDS = 2.0 V, pompa di carica DAC accesa | 48.7 | |||||

| VDDS = 2.0 V, pompa di carica DAC disattivata | 70.2 | |||||

| VDDS = 1.8 V, pompa di carica DAC accesa | 46.3 | |||||

| VDDS = 1.8 V, pompa di carica DAC disattivata | 88.9 | |||||

|

Carico interno: comparatore di tempo continuo/comparatore con clock a basso consumo |

||||||

| Non disponibile | Nonlinearità differenziale | VRIF. = VDDS, carico = Comparatore di tempo continuo o Comparatore con clock a basso consumo FDAC = 250 kHz | ±1 | LSB(1) | ||

| Nonlinearità differenziale | VRIF. = VDDS, carico = Comparatore di tempo continuo o Comparatore con clock a basso consumo FDAC = 16 kHz | ±1.2 | ||||

| Errore di offset(2) Carico = Comparatore temporale continuo | VRIF. = VDD = 3.8 V | ±0.64 | LSB(1) | |||

| VRIF. = VDDS= 3.0 V | ±0.81 | |||||

| VRIF. = VDD = 1.8 V | ±1.27 | |||||

| VRIF. = DCOUPL, precarica ON | ±3.43 | |||||

| VRIF. = DCOUPL, precarica OFF | ±2.88 | |||||

| VRIF. = ADCREF | ±2.37 | |||||

| Errore di offset(2) Carico = comparatore con clock a basso consumo | VRIF. = VDDS= 3.8 V | ±0.78 | LSB(1) | |||

| VRIF. = VDD = 3.0 V | ±0.77 | |||||

| VRIF. = VDDS= 1.8 V | ±3.46 | |||||

| VRIF. = DCOUPL, precarica ON | ±3.44 | |||||

| VRIF. = DCOUPL, precarica OFF | ±4.70 | |||||

| VRIF. = ADCREF | ±4.11 | |||||

| Vol. uscita codice maxtage variazione(2) Carico = Comparatore temporale continuo | VRIF. = VDD = 3.8 V | ±1.53 | LSB(1) | |||

| VRIF. = VDD = 3.0 V | ±1.71 | |||||

| VRIF. = VDDS= 1.8 V | ±2.10 | |||||

| VRIF. = DCOUPL, precarica ON | ±6.00 | |||||

| VRIF. = DCOUPL, precarica OFF | ±3.85 | |||||

| VRIF. = ADCREF | ±5.84 | |||||

Tc = 25 °C, VDDS = 3.0 V, se non diversamente specificato.

|

PARAMETRO |

CONDIZIONI DI PROVA | MIN TIPO MAX |

UNITÀ |

|

| Vol. uscita codice maxtage variazione(2) Carico = comparatore con clock a basso consumo | VRIF. = VDDS= 3.8 V | ±2.92 | LSB(1) | |

| VRIF. =VDDS= 3.0 V | ±3.06 | |||

| VRIF. = VDDS= 1.8 V | ±3.91 | |||

| VRIF. = DCOUPL, precarica ON | ±7.84 | |||

| VRIF. = DCOUPL, precarica OFF | ±4.06 | |||

| VRIF. = ADCREF | ±6.94 | |||

| Volume di uscitatage range(2) Carico = Comparatore temporale continuo | VRIF. = VDDS = 3.8 V, codice 1 | 0.03 | V | |

| VRIF. = VDDS = 3.8 V, codice 255 | 3.62 | |||

| VRIF. = VDDS= 3.0 V, codice 1 | 0.02 | |||

| VRIF. = VDDS= 3.0 V, codice 255 | 2.86 | |||

| VRIF. = VDDS= 1.8 V, codice 1 | 0.01 | |||

| VRIF. = VDDS = 1.8 V, codice 255 | 1.71 | |||

| VRIF. = DCOUPL, precarica OFF, codice 1 | 0.01 | |||

| VRIF. = DCOUPL, precarica OFF, codice 255 | 1.21 | |||

| VRIF. = DCOUPL, precarica ON, codice 1 | 1.27 | |||

| VRIF. = DCOUPL, precarica ON, codice 255 | 2.46 | |||

| VRIF. = ADCREF, codice 1 | 0.01 | |||

| VRIF. = ADCREF, codice 255 | 1.41 | |||

| Volume di uscitatage range(2) Carico = comparatore con clock a basso consumo | VRIF. = VDDS = 3.8 V, codice 1 | 0.03 | V | |

| VRIF. = VDDS= 3.8 V, codice 255 | 3.61 | |||

| VRIF. = VDDS= 3.0 V, codice 1 | 0.02 | |||

| VRIF. = VDDS= 3.0 V, codice 255 | 2.85 | |||

| VRIF. = VDDS = 1.8 V, codice 1 | 0.01 | |||

| VRIF. = VDDS = 1.8 V, codice 255 | 1.71 | |||

| VRIF. = DCOUPL, precarica OFF, codice 1 | 0.01 | |||

| VRIF. = DCOUPL, precarica OFF, codice 255 | 1.21 | |||

| VRIF. = DCOUPL, precarica ON, codice 1 | 1.27 | |||

| VRIF. = DCOUPL, precarica ON, codice 255 | 2.46 | |||

| VRIF. = ADCREF, codice 1 | 0.01 | |||

| VRIF. = ADCREF, codice 255 | 1.41 | |||

|

Carico esterno |

||||

|

INLANDESE |

Nonlinearità integrale |

VRIF. = VDD, FDAC = 250 kHz | ±1 |

LSB(1) |

| VRIF. = DCOUPL, FDAC = 250 kHz | ±2 | |||

| VRIF. = ADCREF, FDAC = 250 kHz | ±1 | |||

| Non disponibile | Nonlinearità differenziale | VRIF. = VDD, FDAC = 250 kHz | ±1 | LSB(1) |

| Errore di offset | VRIF. = VDDS= 3.8 V | ±0.40 | LSB(1) | |

| VRIF. = VDDS= 3.0 V | ±0.50 | |||

| VRIF. = VDD = 1.8 V | ±0.75 | |||

| VRIF. = DCOUPL, precarica ON | ±1.55 | |||

| VRIF. = DCOUPL, precarica OFF | ±1.30 | |||

| VRIF. = ADCREF | ±1.10 | |||

| Vol. uscita codice maxtage variazione | VRIF. = VDDS= 3.8 V | ±1.00 | LSB(1) | |

| VRIF. = VDDS= 3.0 V | ±1.00 | |||

| VRIF. = VDDS= 1.8 V | ±1.00 | |||

| VRIF. = DCOUPL, precarica ON | ±3.45 | |||

| VRIF. = DCOUPL, precarica OFF | ±2.10 | |||

| VRIF. = ADCREF | ±1.90 | |||

| Volume di uscitatage gamma Carico = comparatore con clock a basso consumo |

VRIF. = VDDS = 3.8 V, codice 1 | 0.03 | V |

- 1 LSB (VREF 3.8 V/3.0 V/1.8 V/DCOUPL/ADCREF) = 14.10 mV/11.13 mV/6.68 mV/4.67 mV/5.48 mV

- Include l'offset del comparatore

- Un carico > 20 pF aumenterà il tempo di assestamento

- Multimetro Keysight 34401A

8.15.3 Monitoraggio della temperatura e della batteria

8.15.3.1 Sensore di temperatura

Misurato su un progetto di riferimento Texas Instruments con Tc = 25 °C, VDDS = 3.0 V, se non diversamente specificato.

| PARAMETRO | CONDIZIONI DI PROVA | MINIMO | TIPO | Massimo |

UNITÀ |

| Risoluzione | 2 | °C | |||

| Precisione | da -40 °C a 0 °C | ±5.0 | °C | ||

| Precisione | da 0 °C a 105 °C | ±3.5 | °C | ||

| Volume di fornituratage coefficiente(1) | 3.6 | °C/V | |||

- Il sensore di temperatura viene compensato automaticamente per la variazione VDDS quando si utilizza il driver di temperatura fornito da TI.

8.15.3.2 Monitoraggio della batteria

Misurato su un progetto di riferimento Texas Instruments con T = 25 °C, se non diversamente specificato.

|

PARAMETRO |

CONDIZIONI DI PROVA | MINIMO | TIPO | Massimo |

UNITÀ |

| Risoluzione | 25 | mV | |||

| Allineare | 1.8 | 3.8 | V | ||

| Non linearità integrale (max) | 23 | mV | |||

| Precisione | VDD = 3.0 V | 22.5 | mV | ||

| Errore di offset | -32 | mV | |||

| Guadagna errore | -1 | % | |||

8.15.4 Comparatori

8.15.4.1 Comparatore con clock a basso consumo

T = 25 °C, V = 3.0 V, se non diversamente specificato.

| PARAMETRO | CONDIZIONI DI PROVA | MINIMO | TIPO | Massimo |

UNITÀ |

| Ingresso voltage gamma | 0 | VDD | V | ||

| Frequenza di clock | SCLK_LF | ||||

| Riferimento interno voltage(1) | Utilizzando il DAC interno con VDDS come riferimento voltage, codice DAC = 0 – 255 | 0.024 – 2.865 | V | ||

| Offset | Misurato a VDottore in odontoiatria /2, include l'errore del DAC interno | ±5 | mV | ||

| Tempo di decisione | Passa da –50 mV a 50 mV | 1 | Ciclo di clock | ||

(1) Il comparatore può utilizzare un DAC interno a 8 bit come riferimento. L'uscita del DAC voltagL'intervallo dipende dal volume di riferimentotage selezionato. Vedere

8.15.4.2 Comparatore temporale continuo

Tc = 25°C, VDDS = 3.0 V, se non diversamente specificato.

| PARAMETRO | CONDIZIONI DI PROVA | MINIMO | TIPO | Massimo |

UNITÀ |

| Ingresso voltaggamma e(1) | 0 | VDD | V | ||

| Offset | Misurato a VDottore in odontoiatria / 2 | ±5 | mV | ||

| Tempo di decisione | Passa da –10 mV a 10 mV | 0.70 | ms | ||

| Consumo attuale | Riferimento interno | 8.0 | µA | ||

- Il volume di ingressotages possono essere generati esternamente e collegati tramite I/O o un riferimento interno voltage può essere generato utilizzando il DAC

8.15.5 Sorgente corrente

8.15.5.1 Sorgente di corrente programmabile

Tc = 25 °C, VDDS = 3.0 V, se non diversamente specificato.

| PARAMETRO | CONDIZIONI DI PROVA | MINIMO | TIPO | Massimo |

UNITÀ |

| Intervallo di uscita programmabile della sorgente di corrente (intervallo logaritmico) | 0.25 – 20 | µA | |||

| Risoluzione | 0.25 | µA | |||

8.15.6 GPIO

8.15.6.1 Caratteristiche CC GPIO

Misure CBSed a PG2.1:

|

PARAMETRO |

CONDIZIONI DI PROVA | MINIMO | TIPO | Massimo |

UNITÀ |

|

TA = 25°C, VDottore in odontoiatria = 1.8 V |

|||||

| GPIO VOH con carico di 8 mA | IOCURR = 2, solo GPIO ad alta unità | 1.56 | V | ||

| GPIO VOL con carico di 8 mA | IOCURR = 2, solo GPIO ad alta unità | 0.24 | V | ||

| GPIO VOH con carico di 4 mA | IOCORR = 1 | 1.59 | V | ||

| GPIO VOL con carico di 4 mA | IOCORR = 1 | 0.21 | V | ||

| Corrente di pull-up GPIO | Modalità di ingresso, pullup abilitato, Vpad = 0 V | 73 | µA | ||

| Corrente di pulldown GPIO | Modalità di input, pulldown abilitato, Vpad = VDDS | 19 | µA | ||

| Transizione di ingresso GPIO da basso ad alto, con isteresi | IH = 1, transizione voltage per l'ingresso letto come 0 → 1 | 1.08 | V | ||

| Transizione di ingresso GPIO da alto a basso, con isteresi | IH = 1, transizione voltage per l'ingresso letto come 1 → 0 | 0.73 | V | ||

| Isteresi dell'ingresso GPIO | IH = 1, differenza tra 0 → 1 e 1 → 0 punti | 0.35 | V | ||

|

TA = 25°C, VDottore in odontoiatria = 3.0 V |

|||||

| GPIO VOH con carico di 8 mA | IOCURR = 2, solo GPIO ad alta unità | 2.59 | V | ||

| GPIO VOL con carico di 8 mA | IOCURR = 2, solo GPIO ad alta unità | 0.42 | V | ||

| GPIO VOH con carico di 4 mA | IOCORR = 1 | 2.63 | V | ||

| GPIO VOL con carico di 4 mA | IOCORR = 1 | 0.40 | V | ||

|

TA = 25°C, VDottore in odontoiatria = 3.8 V |

|||||

| Corrente di pull-up GPIO | Modalità di ingresso, pullup abilitato, Vpad = 0 V | 282 | µA | ||

| Corrente di pulldown GPIO | Modalità di input, pulldown abilitato, Vpad = VDDS | 110 | µA | ||

| Transizione di ingresso GPIO da basso ad alto, con isteresi | IH = 1, transizione voltage per l'ingresso letto come 0 → 1 | 1.97 | V | ||

| Transizione di ingresso GPIO da alto a basso, con isteresi | IH = 1, transizione voltage per l'ingresso letto come 1 → 0 | 1.55 | V | ||

| Isteresi dell'ingresso GPIO | IH = 1, differenza tra 0 → 1 e 1 → 0 punti | 0.42 | V | ||

| TA = 25 ° C | |||||

| VIH | Vol. ingresso GPIO più bassotage interpretato attendibilmente come a Alto |

0.8*VDottore in odontoiatria | V | ||

| VIOLENZA | Vol. ingresso GPIO più altotage interpretato attendibilmente come a Basso |

0.2*VDottore in odontoiatria | V | ||

8.16 Caratteristiche tipiche

Tutte le misurazioni in questa sezione vengono eseguite con Tc = 25 °C e VDDS = 3.0 V, se non diversamente specificato. Vedere Condizioni operative consigliate per i limiti del dispositivo. I valori che superano questi limiti sono solo di riferimento.

8.16.1 Corrente MCU

8.16.2 Corrente RX

8.16.2 Corrente RX

8.16.3 Corrente TX

Tabella 8-1. Corrente TX tipica e potenza in uscita

| CC1312PSIP a 915 MHz, VDDS = 3.0 V (misurato su LP-EM-CC1312PSIP) | |||

|

txPower |

Impostazione potenza TX (SmartRF Studio) | Potenza di uscita tipica [dBm] |

Consumo di corrente tipico [mA] |

| 0x013F | 14 | 13.8 | 34.6 |

| 0x823F | 12.5 | 12.2 | 24.9 |

| 0x7828 | 12 | 11.8 | 23.5 |

| 0x7A15 | 11 | 10.9 | 21.6 |

| 0x4C0D | 10 | 10.1 | 20.0 |

| 0x400Un | 9 | 9.5 | 19.1 |

| 0x449Un | 8 | 8.1 | 17.1 |

| 0x364D | 7 | 6.8 | 15.3 |

| 0x2892 | 6 | 6.3 | 14.8 |

| 0x20CC | 5 | 4.9 | 13.7 |

| 0x28D8 | 4 | 4 | 12.6 |

| 0x1C46 | 3 | 3.7 | 11.7 |

| 0x18D4 | 2 | 2.8 | 11.5 |

| 0x16D1 | 1 | 0.8 | 10.6 |

| 0x16D0 | 0 | 0.3 | 10.3 |

| 0x0CCB | -3 | -3.4 | 8.6 |

| 0x0CC9 | -5 | -5.4 | 7.9 |

| 0x08C7 | -7 | -8 | 7.3 |

| 0x0AC5 | -10 | -11.7 | 6.6 |

| 0x08C3 | -15 | -17.1 | 5.9 |

| 0x08C2 | -20 | -20.9 | 5.6 |

8.16.4 Prestazioni RX

8.16.5 Prestazioni TX

8.16.5 Prestazioni TX

8.16.6 Prestazioni dell'ADC

8.16.6 Prestazioni dell'ADC

Descrizione dettagliata

9.1 Oltreview

La sezione 4 mostra i moduli principali del dispositivo CC1312PSIP.

9.2 CPU del sistema

-CPU del sistema M4F, che esegue il file

applicazione e gli strati superiori degli stack di protocolli radio.

L'MCU wireless SimpleLink™ CC1312PSIP contiene una corteccia del braccio

La CPU del sistema costituisce la base di una piattaforma ad alte prestazioni e a basso costo che soddisfa i requisiti di sistema di implementazione minima della memoria e basso consumo energetico, offrendo allo stesso tempo prestazioni di calcolo eccezionali e un'eccezionale risposta del sistema agli interrupt.

Le sue caratteristiche includono quanto segue:

- Architettura ARMv7-M ottimizzata per applicazioni embedded di piccolo ingombro

- Il set di istruzioni miste Arm Thumb -2 a 16 e 32 bit offre le elevate prestazioni attese da un core Arm a 32 bit in una dimensione di memoria compatta

- L'esecuzione rapida del codice consente di aumentare la durata della modalità di sospensione

- Gestione degli interrupt deterministica e ad alte prestazioni per applicazioni time-critical

- Istruzione di moltiplicazione a ciclo singolo e divisione hardware

- La divisione hardware e l'elaborazione veloce del segnale digitale si moltiplicano

- Aritmetica di saturazione per l'elaborazione del segnale

- Unità a virgola mobile (FPU) a precisione singola conforme a IEEE 754

- Unità di protezione della memoria (MPU) per applicazioni critiche per la sicurezza

- Debug completo con corrispondenza dei dati per la generazione di watchpoint

– Unità di controllo e tracciamento dati (DWT)

- JTAG Porta di accesso debug (DAP)

– Unità Flash Patch e Breakpoint (FPB) - Il supporto della traccia riduce il numero di pin richiesti per il debug e la traccia

– Strumentazione Unità traccia macrocellula (ITM)

– Trace Port Interface Unit (TPIU) con uscita seriale asincrona (SWO) - Ottimizzato per l'accesso alla memoria flash a ciclo singolo

- Strettamente connesso alla cache di sostituzione casuale a 8 vie da 4 KB per un consumo energetico attivo e stati di attesa minimi

- Consumo energetico estremamente basso con modalità di sospensione integrate

- Funzionamento a 48 MHz

- 1.25 DMIPS per MHz

9.3 Radio (nucleo RF)

RF Core è un modulo radio altamente flessibile e a prova di futuro che contiene un processore Arm Cortex-M0 che interfaccia i circuiti RF analogici e in banda base, gestisce i dati da e verso il lato CPU del sistema e assembla i bit di informazioni in un determinato pacchetto struttura. Il core RF offre un'API di alto livello basata su comandi alla CPU principale attraverso la quale vengono trasmessi configurazioni e dati. Il processore Arm Cortex-M0 non è programmabile dai clienti ed è interfacciato tramite il driver RF fornito da TI incluso nel kit di sviluppo software SimpleLink (SDK).

Il core RF può gestire autonomamente gli aspetti critici in termini di tempo dei protocolli radio, scaricando così la CPU principale, riducendo la potenza e lasciando più risorse per l'applicazione dell'utente. Sono inoltre disponibili diversi segnali per controllare in modo autonomo circuiti esterni come interruttori RF o range extender.

I vari formati radio del livello fisico sono in parte costruiti come una radio definita dal software in cui il comportamento della radio è definito dai contenuti della ROM radio o da formati radio non ROM forniti sotto forma di patch firmware con gli SDK SimpleLink. Ciò consente di aggiornare la piattaforma radio per supportare le future versioni degli standard anche con aggiornamenti over-the-air (OTA), pur utilizzando lo stesso silicio.

Nota

Non tutte le combinazioni di funzionalità, frequenze, velocità dati e formati di modulazione descritte in questo capitolo sono supportate. Nel corso del tempo, TI può abilitare nuovi formati radio fisici (PHY) per il dispositivo e fornire numeri di prestazione per PHY selezionati nella scheda tecnica. I formati radio supportati per un dispositivo specifico, comprese le impostazioni ottimizzate da utilizzare con il driver RF TI, sono inclusi nello strumento SmartRF Studio con i numeri delle prestazioni dei formati selezionati disponibili nella sezione Specifiche.

9.3.1 Formati radio proprietari

La radio CC1312PSIP può supportare un'ampia gamma di formati radio fisici attraverso una serie di periferiche hardware combinate con il firmware disponibile nella ROM del dispositivo, coprendo le varie esigenze dei clienti per l'ottimizzazione di parametri quali velocità o sensibilità. Ciò consente una grande flessibilità nella sintonizzazione della radio sia per lavorare con protocolli legacy sia per personalizzare il comportamento per esigenze applicative specifiche.

La Tabella 9-1 fornisce una spiegazione semplificataview delle caratteristiche dei vari formati radio disponibili nella ROM. Altri formati radio potrebbero essere disponibili sotto forma di patch o programmi firmware radio tramite il Software Development Kit (SDK) e potrebbero combinare funzionalità in modo diverso, nonché aggiungere altre funzionalità.

Tabella 9-1. Supporto delle funzionalità

|

Caratteristica |

Modalità principale 2-(G)FSK | Velocità dati elevate | Bassa velocità dati |

SimpleLink™ Lungo raggio |

| Preambolo programmabile, parola di sincronizzazione e CRC | SÌ | SÌ | SÌ | NO |

| Larghezza di banda di ricezione programmabile | SÌ | SÌ | Sì (fino a 4 kHz) | SÌ |

| Velocità dati/simboli(3) | Da 20 a 1000 kbps | ≤ 2 Msps | ≤ 100 ksps | ≤ 20 ksps |

| Formato di modulazione | 2-(G)FSK | 2-(G)FSK 4-(G)FSK | 2-(G)FSK 4-(G)FSK | 2-(G)FSK |

| Parola di doppia sincronizzazione | SÌ | SÌ | NO | NO |

| Rilevamento della portante (1) (2) | SÌ | NO | NO | NO |

| Rilevamento del preambolo(2) | SÌ | SÌ | SÌ | NO |

| Sbiancamento dei dati | SÌ | SÌ | SÌ | SÌ |

| RSSI digitale | SÌ | SÌ | SÌ | SÌ |

| Filtraggio CRC | SÌ | SÌ | SÌ | SÌ |

| Spettro diffuso a sequenza diretta (DSSS) | NO | NO | NO | 1:2 1:4 1:8 |

| Correzione degli errori in avanti (FEC) | NO | NO | NO | SÌ |

| Indicatore della qualità del collegamento (LQI) | SÌ | SÌ | SÌ | SÌ |