Dispositivo logico programmabile complesso Atmel ATF15xx

Specifiche

- Nome prodotto: Programmazione in-system Atmel ATF15xx

- Modello: ATF15xx

- Tipo: Dispositivo logico programmabile complesso (CPLD)

- Metodo di programmazione: programmazione in-system (ISP)

- Interfaccia: JTAG Interfaccia ISP

- Produttore: Atmel

Domande frequenti

D: Posso utilizzare software di programmazione di terze parti con i CPLD ATF15xx?

A: Sì, a patto che il software supporti l'algoritmo di programmazione e JTAG istruzioni necessarie per i CPLD ATF15xx.

D: È possibile programmare più CPLD ATF15xx contemporaneamente?

A: Sì, la JTAG L'interfaccia ISP supporta la programmazione di più dispositivi per una programmazione efficiente di più CPLD contemporaneamente.

Introduzione

- I dispositivi logici programmabili complessi (CPLD) Atmel® ATF15xx con architettura Logic Doubling® supportano la programmazione in-system (ISP) tramite il Joint Test Action Group (J) IEEE Std. 1149.1TAG). Questa funzionalità migliora la flessibilità di programmazione e offre vantaggi in varie fasi: sviluppo del prodotto, produzione e utilizzo sul campo. Questa guida utente descrive i metodi di progettazione e i requisiti per l'implementazione di ISP su CPLD ATF15xx con supporto ISP come elencato di seguito:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

Caratteristiche e vantaggi

La programmazione in-system consente la programmazione e la riprogrammazione dei dispositivi ISP dopo il loro montaggio sui circuiti stampati (PCB). Ciò elimina la fase di gestione aggiuntiva richiesta nel processo di produzione per programmare i dispositivi su un programmatore di dispositivi esterno prima che vengano montati sui PCB. L'eliminazione di questa fase riduce la possibilità di danneggiare i delicati cavi dei dispositivi a montaggio superficiale con elevato numero di pin o di danneggiare il dispositivo tramite scariche elettrostatiche (ESD) durante il flusso di programmazione. ISP consente inoltre agli utenti di apportare modifiche di progettazione e aggiornamenti sul campo senza dover rimuovere i dispositivi ISP dai PCB. Inoltre, consente anche l'uso di un microcontrollore incorporato o di un tester in-circuit per eseguire operazioni di programmazione in-system sui dispositivi ISP e integrare queste operazioni di programmazione nel flusso di produzione dei circuiti stampati.

Sistemi di programmazione in-system

I tre componenti essenziali di un sistema ISP per i CPLD ATF15xx sono:

Software

Implementazione dell'algoritmo di programmazione, nonché generazione del JTAG istruzioni e dati per i dispositivi ISP di destinazione. Può trattarsi di un programma software in esecuzione su un PC, un microcontrollore incorporato o un'apparecchiatura di collaudo in-circuit.

Interfaccia Hardware

Un canale di comunicazione tra il software ISP e i dispositivi ISP sulla scheda target. Può trattarsi di un cavo di download ISP o di un programmatore di Atmel o di un fornitore terzo, di un'apparecchiatura di collaudo in-circuit o delle connessioni tra un microcontrollore incorporato e i dispositivi ISP sul PCB

Scheda bersaglio

Scheda di circuito contenente i dispositivi ISP nel JTAG catena. Può trattarsi della scheda di sviluppo/programmazione CPLD ATF15xx di Atmel o di una scheda di circuito personalizzata con l'appropriato JTAG connessioni all'hardware dell'interfaccia.

Oltre a questi tre componenti, un JEDEC file è necessario programmare un CPLD ATF15xx. Questo JEDEC file può essere creato compilando un design file utilizzando software di sviluppo che supporta i CPLD ATF15xx come Atmel WinCUPL e Atmel ProChip Designer. Atmel fornisce anche un'utilità software di traduzione, POF2JED.exe, che converte l'output file dal formato di programmazione del concorrente a un JEDEC file compatibile con il CPLD ATF15xx. Per maggiori informazioni su questa utility, fare riferimento alla nota applicativa Atmel, “ATF15xx Product Family Conversion”, disponibile su Atmel websito. Dopo il JEDEC files sono creati per tutti i CPLD ATF15xx, possono essere programmati sulla scheda target. I CPLD ATF15xx possono essere programmati dai seguenti sistemi di programmazione in-system:

- Sistema di programmazione in-system ATF15xx

- Microcontrollori incorporati

- Tester in-circuit

Sistema di programmazione in-system Atmel ATF15xx

Per la programmazione in-system dei CPLD ATF15xx, Atmel mette a disposizione il software ISP, il cavo di download e il kit di sviluppo/programmazione, descritti nelle sezioni seguenti.

Software dell'ISP

Il software Atmel ATF15xx ISP, ATMISP, è il mezzo principale per implementare JTAG programmazione in-system sui CPLD ATF15xx. ATMISP funziona su un PC host basato su Windows e implementa la programmazione in-system dei CPLD ATF15xx sul sistema hardware ISP di destinazione o genera un formato vettoriale seriale (.SVF) file da utilizzare da parte dell'apparecchiatura di collaudo automatico (ATE) per programmare i CPLD ATF15xx sul sistema di destinazione. ATMISP acquisisce prima tutte le informazioni necessarie dagli utenti sul JTAG catena di dispositivi nel sistema di destinazione. Quindi esegue l'appropriato JTAG Istruzioni ISP sul JTAG catena di dispositivi nel sistema di destinazione secondo JTAG informazioni sulla catena di dispositivi specificate dagli utenti tramite la porta USB o LPT del PC. Ulteriori informazioni sul software Atmel ATMISP sono disponibili all'indirizzo www.atmel.com/tools/ATMISP.aspx.

Cavo di download ISP

Il cavo di download ISP basato su USB Atmel ATF15xx, ATDH1150USB, si collega a una porta USB standard di un computer host da un lato e a una porta JTAG header del circuito stampato di destinazione sull'altro lato. Trasferisce il JTAG istruzioni e dati generati da ATMISP in esecuzione sul PC host ai dispositivi ISP sulla scheda di circuito di destinazione. Ulteriori informazioni sul cavo ATDH1150USB sono disponibili all'indirizzo www.atmel.com/tools/ATDH1150USB.aspx.

Sviluppo/Programmatore

Il kit di sviluppo/programmazione Atmel ATF15xx, ATF15xx-DK3-U, è un sistema di sviluppo completo e un programmatore ISP per i CPLD ATF15xx. Questo kit fornisce ai progettisti un modo molto rapido e semplice per sviluppare prototipi e valutare nuovi progetti con un CPLD ISP ATF15xx. Grazie alla disponibilità di diverse schede adattatrici socket per supportare la maggior parte dei tipi di package offerti nei CPLD ATF15xx, questo kit può essere utilizzato come programmatore ISP per programmare i CPLD ISP ATF15xx nella maggior parte dei tipi di package disponibili tramite JTAG interfaccia. Ulteriori informazioni sul kit Atmel ATF15xx-DK3-U sono disponibili all'indirizzo www.atmel.com/tools/ATF15XX-DK3-U.aspx.

Sistema di microcontrollore incorporato

L'algoritmo di programmazione e JTAG le istruzioni per i CPLD ATF15xx possono essere implementate in un microcontrollore o microprocessore, che può quindi essere utilizzato per programmare i CPLD ATF15xx sulla scheda target. Un metodo possibile è quello di estrarre tutti i J pertinentiTAG informazioni sul protocollo (ad esempio JTAG istruzioni e dati) dalla SVF file generato dal software ATMISP, e quindi utilizzare queste informazioni per implementare il codice per il microcontrollore o microprocessore che genererebbe il JTAG segnali per i dispositivi ISP nel JTAG chain. Questo approccio è più adatto per sistemi che hanno già un microcontrollore o un microprocessore incorporato, e questo elimina l'uso di software di programmazione e strumenti hardware esterni nel sistema.

Sistema di test in circuito

I CPLD ATF15xx possono essere programmati sulla scheda di circuito di destinazione tramite JTAG interfaccia durante il test della scheda di circuito utilizzando un tester in-circuit. In genere, l'SVF file generato da ATMISP dovrebbe contenere tutti i J pertinentiTAG informazioni di programmazione in-system di cui i tester in-circuit hanno bisogno per programmare i CPLD ATF15xx sulla scheda di circuito target. Questo approccio consente l'integrazione della fase di programmazione nel testing stage del flusso produttivo.

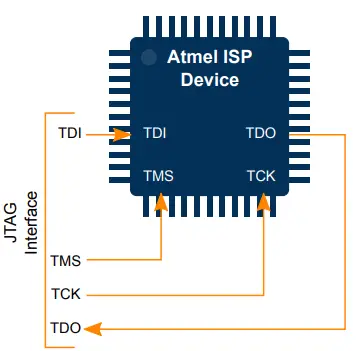

JTAG Interfaccia ISP

L'ISP per i CPLD ATF15xx è implementato utilizzando lo standard IEEE 1149.1 Std. JTAG interfaccia. Questa interfaccia può essere utilizzata per cancellare, programmare e verificare i CPLD ATF15xx. La JTAG l'interfaccia è un'interfaccia seriale costituita dai segnali TCK, TMS, TDI e TDO e da un JTAG Controller Test Access Port (TAP). Il pin TCK è l'ingresso di clock per JTAG Controllo TAP e per cambiare dentro/fuori la JTAG istruzioni e dati. Il pin TDI è l'input dati seriale. Viene utilizzato per spostare istruzioni di programmazione e dati nei dispositivi ISP. Il pin TDO è l'output dati seriale. Viene utilizzato per spostare dati dai dispositivi ISP. Il pin TMS è un pin di selezione modalità. Controlla lo stato del JTAG Regolatore TAP. Il JTAG pin di interfaccia del CPLD ATF15xx sulla scheda di destinazione ISP devono essere collegati all'hardware di interfaccia ISP (ad esempio il cavo di download ISP) in genere tramite un header a 10 pin. L'hardware di interfaccia ISP deve anche essere collegato al PC host che esegue il software ISP. L'hardware di interfaccia ISP stabilisce la comunicazione tra il software ISP e i dispositivi ISP e consente al software ISP di trasferire le istruzioni di programmazione e i dati dal PC host ai CPLD ATF15xx. I CPLD ATF15xx con JTAG le funzionalità abilitate sono completamente JTAG compatibile e supporta anche le operazioni Boundary Scan Test (BST) richieste specificate nel JTAG standard. I CPLD ATF15xx possono essere configurati per essere parte di un JTAG Catena BST con altri JTAG dispositivi per il test in-circuit della scheda di sistema. Con questa caratteristica, i CPLD ATF15xx possono essere testati sulla scheda di circuito insieme ad altri JTAG-dispositivi supportati senza ricorrere ai test del letto d'aghi.

Programmazione di un singolo dispositivo

Il JTAG L'interfaccia ISP può essere configurata per programmare un singolo CPLD ATF15xx. Il JTAG configurazione per un singolo dispositivo è mostrata nella figura sottostante. Quando un CPLD ATF15xx è configurato in questo modo, un registro appare tra i pin TDI e TDO del dispositivo. La dimensione del registro dipende dal JTAG larghezza dell'istruzione e i dati che vengono spostati per quell'istruzione. Figura 2-1 JTAG Dispositivo

Programmazione di più dispositivi

I CPLD ATF15xx possono essere configurati come parte di una catena a margherita di più JTAG-dispositivi supportati come descritto di seguito e mostrato anche nella figura seguente.

- Collegare il pin TMS e TCK per ciascun dispositivo nel JTAG catena ai pin TMS e TCK del JTAG intestazione dell'interfaccia sul circuito stampato.

- Collegare il pin TDI del primo dispositivo al pin TDI del JTAG intestazione dell'interfaccia.

- Collega il pin TDO del primo dispositivo al pin TDI del dispositivo successivo. Continua questo processo finché tutti tranne l'ultimo sono collegati.

- Collegare il pin TDO dell'ultimo dispositivo al pin TDO del JTAG intestazione dell'interfaccia.

Figura 2-2 Dispositivo multiplo JTAG Configurazione

Per programmare più dispositivi in un JTAG chain, gli utenti devono utilizzare strumenti software ISP che supportano tali funzionalità. Nel software ISP, gli utenti devono specificare:

- Numero di dispositivi nella JTAG catena.

- Numeri di parte dei dispositivi e posizioni all'interno della JTAG catena.

- JTAG operazioni per ciascuno dei dispositivi.

- Altro JTAG- informazioni correlate come la JTAG larghezza delle istruzioni per ciascuno dei dispositivi.

Una volta la JTAG la catena a margherita è impostata correttamente sulla scheda di destinazione ISP e nel software ISP, i dispositivi nel JTAG la catena può essere programmata contemporaneamente.

Considerazioni sulla progettazione

Per eseguire ISP su un CPLD ATF15xx, risorse per JTAG interfaccia nell'ATF15xx deve essere riservata. Pertanto, i quattro pin I/O per i pin TMS, TDI, TDO e TCK devono essere riservati per JTAG e non possono essere utilizzati come I/O utente. I numeri di pin per questi pin dipendono dal CPLD ATF15xx utilizzato e dal tipo di package. Fare riferimento alla tabella sottostante per informazioni sul pinout. Il JTAG lo standard raccomanda che i pin TMS e TDI vengano estratti per ciascun dispositivo nel JTAG catena. I CPLD ATF15xx hanno una funzione pull-up interna per questi pin che, se abilitata, evita la necessità di resistori pull-up esterni. Inoltre, il JTAG la funzionalità di interfaccia deve essere abilitata per eseguire ISP sui CPLD ATF15xx. Abilitare la funzione JTAG interfaccia richiede la scelta di specifici tipi di dispositivi Atmel o impostazioni di opzioni prima di compilare il progetto ATF15xx. Queste procedure sono descritte per WinCUPL, ProChip Designer e POF2JED in questa guida. Per impostazione predefinita, tutti i nuovi CPLD ATF15xx vengono spediti con JTAG interfaccia abilitata. Una volta che le risorse logiche per JTAG sono riservate, gli utenti possono programmare, verificare e cancellare qualsiasi CPLD ATF15xx sulla scheda di destinazione utilizzando il software ATMISP.

Mancia: Sebbene le quattro JTAG i pin sono riservati per un JTAG interfaccia, gli utenti possono implementare funzioni logiche nascoste nelle macrocelle associate a questi pin.

Tabella 3-1 ATF15xx CPLD JTAG Numeri pin

| JTAG Spillo | 44-QFP | 44-PLCC | 84-PLCC | 100-QFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| Stimolazione magnetica | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

Abilita JTAG Interfaccia con WinCUPL

Per abilitare la JTAG interfaccia con WinCUPL, il tipo di dispositivo ISP ATF15xx appropriato deve essere specificato prima che un progetto venga compilato. Dopo che un progetto è stato compilato correttamente, un JEDEC file con la JTAG viene generata la funzionalità di interfaccia abilitata. Quando questo JEDEC file è programmato in un ATF15xxCPLD, il suo JTAG l'interfaccia è abilitata. Gli utenti possono anche abilitare i resistori pull-up interni TDI e TMS includendo le seguenti dichiarazioni di proprietà nel progetto CUPL file.

- PROPRIETÀ ATMEL {TDI_PULLUP = ON};

- PROPRIETÀ ATMEL {TMS_PULLUP = ON};

Avviso: Se un tipo di dispositivo ISP ATF15xx viene utilizzato per un progetto che utilizza JTAG pin di interfaccia come pin di I/O logici, WinCUPL genera un errore.

Nei passaggi seguenti viene illustrato come aprire un progetto esistente in WinCUPL, specificare il tipo di dispositivo e compilare il progetto.

- Nel menu principale di WinCUPL, selezionare File > Apri. Seleziona la sorgente CUPL (.pld) file dalla directory di lavoro appropriata.

- Selezionare OK per aprire la sorgente PLD file.

- Nel menu principale di WinCUPL, selezionare File > Salva. Questo salva le modifiche apportate alla sorgente file.

- Nel menu principale, seleziona Opzioni > Dispositivi. Si apre la finestra di dialogo Selezione dispositivo.

- Scegli il dispositivo ISP ATF15xx appropriato. Consulta la seguente tabella per un elenco di tutti i tipi di dispositivi ATF15xx supportati da WinCUPL.

- Selezionare OK per chiudere il menu di selezione del dispositivo.

- Nota: un metodo alternativo consiste nello scegliere un tipo di dispositivo ATF15xx appropriato dalla seguente tabella e includerlo nella sezione dell'intestazione della sorgente CUPL file.

- Nel menu principale di WinCUPL, selezionare Esegui > Compilazione dipendente dal dispositivo.

- WinCUPL compila il progetto e genera l'Atmel device fitter. Se il progetto è compatibile, un JEDEC file viene creato automaticamente.

- Quando il JEDEC file è programmato nel dispositivo, il JTAG interfaccia, i pull-up TMS e TDI interni opzionali e i circuiti pin-keeper opzionali sono abilitati.

Nota: La selezione di un tipo di dispositivo Atmel ISP abilita automaticamente JTAG interfaccia predefinita quando Atmel WinCUPL esegue Atmel Device Fitter.

Se i progetti impediscono di riservare risorse per la JTAG interfaccia o un ISP non è facoltativamente utilizzato, deve essere selezionato un tipo di dispositivo Atmel non-ISP. Vedere la tabella seguente per un elenco di dispositivi. Il dispositivo può quindi essere riprogrammato utilizzando un programmatore di dispositivi esterno. La tabella seguente elenca i tipi di dispositivo Atmel ISP e Atmel non-ISP per WinCUPL.

Tabella 3-2 Tipo di dispositivo WinCUPL ATF15xx

| Nome dispositivo | Tipo di pacchetto | Tipo di dispositivo WinCUPL | |

| JTAG Abilitato | JTAG Disabilitato | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | Codice articolo F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | Codice articolo: F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | Codice articolo F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | Codice articolo: F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | Codice articolo F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | Codice articolo: F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | Codice articolo F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | Codice articolo: F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | Modello F1508QFP100 |

Abilita JTAG Interfaccia con Atmel ProChip Designer

Per abilitare la JTAG interfaccia con ProChip Designer:

- Aprire il progetto ProChip Designer appropriato.

- Aprire la finestra Opzioni Fitter cliccando sul pulsante Atmel Fitter in Device Fitter.

- Selezionare la scheda Dispositivo globale e quindi selezionare JTAG Casella porta. I resistori pull-up interni TMS e TDI possono anche essere abilitati selezionando le caselle TDI Pullup e TMS Pullup. Queste caselle di controllo sono mostrate nella figura sottostante.

Figura 3-1 Interfaccia utente delle opzioni di ProChip Designer Fitter

Abilita JTAG Interfaccia con POF2JED

In POF2JED, il JTAG L'opzione Modalità può essere impostata su Auto per consentire a POF2JED di determinare se JTAG la funzionalità nell'ATF15xx dovrebbe essere abilitata o meno, e si basa sul fatto che JTAG è supportato nel CPLD del concorrente. Per attivare JTAG nel CPLD ATF15xx indipendentemente dal fatto che JTAG è supportato o meno nel CPLD del concorrente, il JTAG L'opzione Modalità dovrebbe essere impostata su On. Quando JTAG è abilitato nell'ATF15xx, le resistenze pull-up interne TDI e TMS possono essere abilitate selezionando Abilita

Caselle TDI_PULLUP e Enable TMS_PULLUP in POF2JED. Vedere la figura sottostante.

Figura 3-2 Interfaccia utente POF2JED

Linee guida e raccomandazioni

Attenzione: Si dovrebbe prestare particolare attenzione a questa sezione quando si eseguono operazioni ISP su CPLD ATF15xx. Questa sezione discute alcuni dei JTAG Linee guida, informazioni e raccomandazioni degli ISP che è opportuno tenere ben presenti.

- Assicurati che JTAG porta per tutti i dispositivi nella JTAG la catena è abilitata.

- Per i CPLD ATF15xx, il JTAG la porta è abilitata se i dispositivi sono vuoti/cancellati o programmati con JTAG abilitato.

- Tutti i dispositivi Atmel ATF15xx vengono spediti nello stato vuoto/cancellato; pertanto, il JTAG la porta è abilitata per tutti i nuovi dispositivi ed è pronta per l'ISP.

- Dispositivi ATF15xx con JTAG disabilitato deve essere cancellato utilizzando un programmatore di dispositivi non ISP per riattivare JTAG porta.

- Assicurarsi che il volume VCC sia correttotage viene applicato a ciascuno dei dispositivi nel JTAG catena.

- CPLD ATF15xxAS/ASL nei tipi di package 84-PLCC, 100-TQFP e 100-PQFP: VCCINT deve essere compreso tra 4.5 V e 5.5 V mentre VCCIO può essere compreso tra 3.0 V e 3.6 V oppure tra 4.5 V e 5.5 V.

- CPLD ATF15xxAS/ASL nei tipi di package 44-PLCC e 44-TQFP: VCC deve essere compresa tra 4.5 V e 5.5 V.

- CPLD ATF15xxASV/ASVL: VCC (VCCIO e VCCINT) deve essere compresa tra 3.0 V e 3.6 V.

- Il VCC per i dispositivi nella JTAG la catena deve essere opportunamente regolata e filtrata.

- Per i CPLD ATF15xx utilizzati nella maggior parte delle applicazioni, si consiglia di utilizzare un condensatore di disaccoppiamento da 0.22 µF per ciascuna delle coppie VCC/GND.

- Si consiglia di utilizzare una messa a terra comune per tutti i dispositivi nel JTAG catena e la JTAG hardware di interfaccia (ad esempio cavo di download ISP ATDH1150USB).

- Si consiglia di evitare lunghi (non più di cinque dispositivi) JTAG catene.

- Se una lunga JTAG chain è necessario, bufferizzare i segnali TMS e TCK dopo ogni quinto dispositivo. Si preferisce l'uso del buffer di trigger Schmitt.

- I buffer rimodellano i tempi di salita e discesa dei segnali TMS e TCK.

- Bisogna tenere in considerazione il ritardo aggiuntivo causato dai buffer.

- Si consiglia di utilizzare resistori pull-up (da 4.7 KΩ a 10 KΩ) per i segnali TMS e TDI e resistori pull-down per il segnale TCK a JTAG intestazione per evitare che questi segnali rimangano fluttuanti quando non sono gestiti dall'hardware dell'interfaccia.

- Per i CPLD ATF15xx sono disponibili pull-up interni opzionali su TMS e TDI.

- Si consiglia di terminare JTAG segnali al JTAG intestazione.

- Sono accettabili sia le terminazioni attive che quelle passive; tuttavia, è preferibile la terminazione passiva.

- Riduce le risonanze causate da lunghe lunghezze di cavi/tracce PCB.

- La terminazione è un aspetto estremamente critico per TMS e TCK.

- Si raccomanda che tutti gli ingressi e gli I/O dei dispositivi nella JTAG catena, eccetto la JTAG pin, dovrebbero essere in uno stato statico quando i CPLD ATF15xx vengono programmati per ridurre al minimo il rumore.

- Quando si utilizza una delle schede di sviluppo/programmazione Atmel ATF15xx, è necessario disattivare l'alimentazione della scheda quando si modificano le posizioni dei ponticelli di selezione VCC.

- Per i CPLD ATF15xx, JTAG L'ISP è disponibile quando il componente è in modalità di spegnimento controllato da pin o quando il dispositivo "a basso consumo" è in modalità di sospensione.

- Stato del dispositivo dopo l'interruzione dell'ISP:

- Se l'ISP viene interrotto, tutti i pin I/O sono tri-state, indipendentemente dallo stato dei circuiti Pin-keeper.

- Impedisce ai dispositivi parzialmente programmati di causare conflitti sul bus con altri dispositivi sulla scheda di circuito.

- Durante la programmazione ISP, tutti i pin I/O si trovano in una delle seguenti condizioni:

- Stato ad alta impedenza:

- Quando viene programmato un dispositivo vuoto/cancellato.

- Quando un dispositivo viene riprogrammato con i circuiti Pin-keeper disabilitati.

- Evita la contesa del bus con dispositivi esterni che interagiscono con i CPLD ATF15xx sulla scheda del circuito.

- Debolmente agganciato allo stato precedente:

- Quando un dispositivo programmato viene riprogrammato con i circuiti Pin-keeper abilitati.

- I pin I/O mantengono i livelli logici precedenti all'ISP.

- Impedisce all'ISP di influenzare il funzionamento di altri dispositivi sulla scheda di sistema.

- L'uso di più JTAG non è consigliabile utilizzare catene su una sola tavola.

- I dispositivi possono interagire tra loro in modo diversoTAG catene.

- La scheda è funzionale solo quando tutti i dispositivi in tutti i JTAG le catene sono programmate con successo.

- Se la programmazione fallisce per almeno un dispositivo in una catena mentre altri JTAG le catene sono state programmate con successo:

- Sia Atmel che altri dispositivi a bordo possono danneggiarsi a causa di possibili problemi di contesa del bus per le uscite a tre stati.

- Lo stato operativo della scheda di sistema non è definito e pertanto potrebbe verificarsi un funzionamento non corretto.

- Inserimento di circuiti attivi tra JTAG intestazione e JTAG dispositivi in catena non è consigliato. Se il circuito attivo non funziona correttamente, potrebbe causare problemi di programmazione/verifica.

- L'uso di volumi mistitage dispositivo JTAG non è consigliabile utilizzare catene.

- Questi sono JTAG catene con dispositivi che utilizzano diversi volumi VCCtage/o interfaccia voltages.

- Interfaccia voltagI livelli (VIL, VIH, VOL, VOH) per i dispositivi a 5.0 V potrebbero non essere compatibili con l'interfaccia voltage livelli per dispositivi da 3.0 V.

- Se ATMISP ha problemi di comunicazione con JTAG catena hardware del dispositivo, provare a eseguire la calibrazione automatica o la calibrazione manuale per abbassare le frequenze del JTAG segnali.

- Assicurati che il LED sul cavo ATDH1150USB sia acceso e verde prima di iniziare la programmazione. Assicurati che il cavo di download ISP sia in grado di comunicare correttamente con il software ATMISP.

- Assicurarsi che il volume VCC sia correttotage viene applicato al cavo ATDH1150USB.

- Il VCC utilizzato dal primo dispositivo nella JTAG la catena deve essere fornita al cavo ATDH1150USB tramite il pin 4 del J a 10 pinTAG intestazione.

- Per i CPLD ATF15xx con VCCINT e VCCIO separati, VCCIO deve essere utilizzato per il cavo ATDH1150USB.

Informazioni per l'ordinazione

| Codice di ordinazione | Descrizione |

| Modello ATF15xx-DK3-U | Kit di sviluppo/programmazione CPLD (include ATF15xxDK3-SAA44 e ATDH1150USB o ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | Scheda adattatore socket TQFP a 100 pin per scheda DK3 |

| ATF15xxDK3-SAJ44 | Scheda adattatore presa PLCC a 44 pin per scheda DK3 |

| ATF15xxDK3-SAJ84 | Scheda adattatore presa PLCC a 84 pin per scheda DK3 |

| ATF15xxDK3-SAA44 | Scheda adattatore socket TQFP a 44 pin per scheda DK3 |

| Modello ATDH1150USB | J basato su USB Atmel ATF15xx CPLDTAG Cavo di download ISP |

Cronologia delle revisioni

| Doc. rev. | Data | Commenti |

| A | 12/2015 | Rilascio documento iniziale. |

INFORMAZIONI SUI CONTATTI

Società Atmel

- 1600 Technology Drive, San Jose, CA 95110 Stati Uniti

- T: (+1)(408) 441.0311

- F: (+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-8968A-CPLD-ATF-ISP_Guida per l'utente-12/2015

Atmel®, il logo Atmel e le relative combinazioni, Enabling Unlimited Possibilities® e altri sono marchi registrati o marchi commerciali di Atmel Corporation negli Stati Uniti e in altri paesi. Altri termini e nomi di prodotti potrebbero essere marchi commerciali di altri.

DISCLAIMER: Le informazioni contenute in questo documento sono fornite in relazione ai prodotti Atmel. Nessuna licenza, espressa o implicita, preclusione o altro, a qualsiasi diritto di proprietà intellettuale è concessa dal presente documento o in connessione con la vendita di prodotti Atmel. SALVO QUANTO PREVISTO NEI TERMINI E CONDIZIONI DI VENDITA LOCALI ATMEL WEBSITO, ATMEL NON SI ASSUME ALCUNA RESPONSABILITÀ E DECLINA QUALSIASI GARANZIA ESPLICITA, IMPLICITA O STATUTARIA RELATIVA AI SUOI PRODOTTI, INCLUSA, SENZA LIMITAZIONE, LA GARANZIA IMPLICITA DI COMMERCIABILITÀ, IDONEITÀ PER UNO SCOPO PARTICOLARE O NON VIOLAZIONE. IN NESSUN CASO ATMEL SARÀ RESPONSABILE PER DANNI DIRETTI, INDIRETTI, CONSEGUENTI, PUNITIVI, SPECIALI O ACCIDENTALI (INCLUSI, SENZA LIMITAZIONE, DANNI PER PERDITE E PROFITTI, INTERRUZIONE DELL'ATTIVITÀ O PERDITA DI INFORMAZIONI) DERIVANTI DALL'USO O DALL'IMPOSSIBILITÀ DI UTILIZZARE QUESTO DOCUMENTO, ANCHE SE ATMEL È STATA INFORMATA DELLA POSSIBILITÀ DI TALI DANNI. Atmel non rilascia dichiarazioni o garanzie in merito all'accuratezza o completezza del contenuto di questo documento e si riserva il diritto di apportare modifiche alle specifiche e alle descrizioni dei prodotti in qualsiasi momento senza preavviso. Atmel non si impegna ad aggiornare le informazioni qui contenute. Salvo diversamente specificato, i prodotti Atmel non sono adatti e non devono essere utilizzati in applicazioni automobilistiche. I prodotti Atmel non sono destinati, autorizzati o garantiti per l'uso come componenti in applicazioni destinate a supportare o sostenere la vita. ESCLUSIONE DI RESPONSABILITÀ PER APPLICAZIONI CRITICHE PER LA SICUREZZA, MILITARI E AUTOMOBILISTICHE: i prodotti Atmel non sono progettati e non saranno utilizzati in relazione ad applicazioni in cui il guasto di tali prodotti potrebbe ragionevolmente causare lesioni personali significative o morte ("Applicazioni critiche per la sicurezza") senza il consenso scritto specifico di un funzionario Atmel. Le applicazioni critiche per la sicurezza includono, senza limitazioni, dispositivi e sistemi di supporto vitale, apparecchiature o sistemi per il funzionamento di impianti nucleari e sistemi di armi. I prodotti Atmel non sono progettati né destinati all'uso in applicazioni o ambienti militari o aerospaziali, a meno che non siano specificamente designati da Atmel come di livello militare. I prodotti Atmel non sono progettati né destinati all'uso in applicazioni automobilistiche, a meno che non siano specificamente indicati da Atmel come di qualità automobilistica.

Documenti / Risorse

|

Dispositivo logico programmabile complesso Atmel ATF15xx [pdf] Guida utente ATF15xx, ATF15xx Dispositivo logico programmabile complesso, Dispositivo logico programmabile complesso, Dispositivo logico programmabile, Dispositivo logico, Dispositivo |